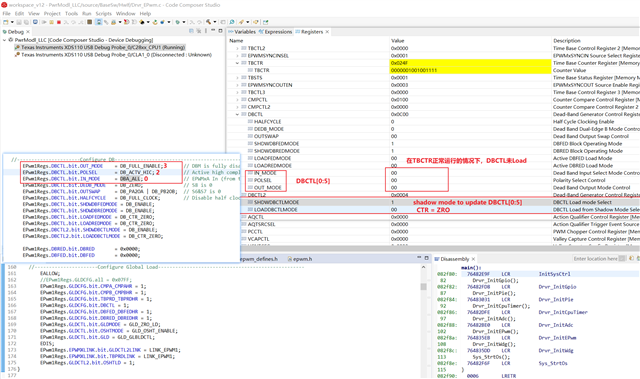

DB死区模块 DBCTL[5:0]可以通过DBCTL2配置为shadow load,以及选择在CTR=ZRO的时刻进行load,但是没有调试显示没有load成功,进而影响了发波

还配置了GLDCTL2来全局加载DBCTL,其他的TBPRD都是可以成功加载的,以下是我的寄存器代码配置:(代码中关于DC和TZ的代码配置可忽略)

void Drvr_EPwm1RegCfg(void)

{

//----------------------Enable clock---------------------------------------------------

EALLOW;

CpuSysRegs.PCLKCR2.bit.EPWM1 = 1; // ePWM1 clock

EDIS;

//----------------------Configure TB---------------------------------------------------

EPwm1Regs.TBPRD = LLC_SWT_UP_PRD; // Set timer period

EPwm1Regs.TBPHS.bit.TBPHS = 0x0000; // Phase is 0

EPwm1Regs.TBCTR = 0x0000; // Clear counter

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP; // Count up mode

EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; // Disable phase loading

EPwm1Regs.TBCTL.bit.PHSDIR = TB_UP; // Phase Direction

EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EPwm1Regs.TBCTL.bit.PRDLD = TB_SHADOW; // shadow mode

EPwm1Regs.TBCTL2.bit.PRDLDSYNC = TB_CTR_ZERO_ONLY; // Shadow to Active Load of TBPRD occurs only when TBCTR = 0

EPwm1Regs.EPWMSYNCOUTEN.bit.ZEROEN = SYNC_OUT_SRC_ENABLE; //This bit enables the TBCTR = 0x0000 event to set the EPWMxSYNCOUT signal.

//----------------------Configure CC---------------------------------------------------

EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; // CMPA shadow mode enable

EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW; // CMPB shadow mode enable

EPwm1Regs.CMPCTL.bit.LOADASYNC = CC_LD_ONLY; // CMPA shadow to active occurs according to LOADMODE

EPwm1Regs.CMPCTL.bit.LOADBSYNC = CC_LD_ONLY; // CMPB shadow to active occurs according to LOADMODE

EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // CMPA Load registers every ZERO

EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO; // CMPB Load registers every ZERO

EPwm1Regs.CMPA.bit.CMPA = EPwm1Regs.TBPRD / 2;

//----------------------Configure AQ---------------------------------------------------

EPwm1Regs.AQCTL.bit.SHDWAQAMODE = AQ_SHADOW; // AQA Shadow mode enable

EPwm1Regs.AQCTL.bit.LDAQASYNC = AQ_LD_ONLY; // AQA shadow to active occurs by loadmode

EPwm1Regs.AQCTL.bit.LDAQAMODE = AQ_CTR_ZERO; // AQA Load registers every ZERO

EPwm1Regs.AQCTLA.bit.ZRO = AQ_SET; // ZERO set

EPwm1Regs.AQCTLA.bit.CAU = AQ_CLEAR; // CMPA up clear

//----------------------Configure DB---------------------------------------------------

EPwm1Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; // DBM is fully disabled or by-passed.

EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC; // Active high complementary (AHC). EPWMxB is inverted.

EPwm1Regs.DBCTL.bit.IN_MODE = DBA_ALL; // EPWMxA In (from the action-qualifier) is the source for both falling-edge and rising-edge delay.

EPwm1Regs.DBCTL.bit.DEDB_MODE = DB_ZERO; // S8 is 0

EPwm1Regs.DBCTL.bit.OUTSWAP = DB_PA2OA | DB_PB2OB; // S6&S7 is 0

EPwm1Regs.DBCTL.bit.HALFCYCLE = DB_FULL_CLOCK; // Disable half clock

EPwm1Regs.DBCTL.bit.SHDWDBFEDMODE = DB_ENABLE;

EPwm1Regs.DBCTL.bit.SHDWDBREDMODE = DB_ENABLE;

EPwm1Regs.DBCTL.bit.LOADFEDMODE = DB_CTR_ZERO;

EPwm1Regs.DBCTL.bit.LOADREDMODE = DB_CTR_ZERO;

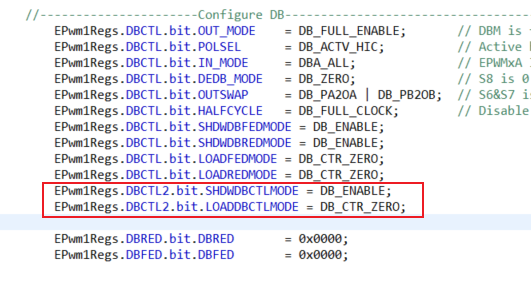

EPwm1Regs.DBCTL2.bit.SHDWDBCTLMODE = DB_ENABLE;

EPwm1Regs.DBCTL2.bit.LOADDBCTLMODE = DB_CTR_ZERO;

EPwm1Regs.DBRED.bit.DBRED = 0x0000;

EPwm1Regs.DBFED.bit.DBFED = 0x0000;

//----------------------Configure DC---------------------------------------------------

EALLOW;

EPwm1Regs.DCACTL.bit.EVT1SRCSEL = DC_EVT1;

EPwm1Regs.DCACTL.bit.EVT1FRCSYNCSEL = DC_EVT_ASYNC;

EPwm1Regs.DCTRIPSEL.bit.DCAHCOMPSEL = 0xF; // Trip combination input

EPwm1Regs.DCAHTRIPSEL.bit.TRIPINPUT4 = 1; // Trip Input 4 selected as combinational ORed input to DCAH mux.

EPwm1Regs.DCAHTRIPSEL.bit.TRIPINPUT5 = 1; // Trip Input 5 selected as combinational ORed input to DCAH mux

EPwm1Regs.DCAHTRIPSEL.bit.TRIPINPUT7 = 1; // Trip Input 7 selected as combinational ORed input to DCAH mux

EPwm1Regs.DCAHTRIPSEL.bit.TRIPINPUT8 = 1; // Trip Input 8 selected as combinational ORed input to DCAH mux

EPwm1Regs.DCAHTRIPSEL.bit.TRIPINPUT9 = 1; // Trip Input 9 selected as combinational ORed input to DCAH mux

EPwm1Regs.DCAHTRIPSEL.bit.TRIPINPUT10 = 1; // Trip Input 10 selected as combinational ORed input to DCAH mux

EPwm1Regs.DCAHTRIPSEL.bit.TRIPINPUT11 = 1; // Trip Input 11 selected as combinational ORed input to DCAH mux

EPwm1Regs.DCAHTRIPSEL.bit.TRIPINPUT12 = 1; // Trip Input 12 selected as combinational ORed input to DCAH mux

EPwm1Regs.DCTRIPSEL.bit.DCBHCOMPSEL = 0xF; // Trip combination input

EPwm1Regs.DCBHTRIPSEL.bit.TRIPINPUT4 = 1; // Trip Input 4 selected as combinational ORed input to DCBH mux.

EPwm1Regs.DCBHTRIPSEL.bit.TRIPINPUT5 = 1; // Trip Input 5 selected as combinational ORed input to DCBH mux

EPwm1Regs.DCBHTRIPSEL.bit.TRIPINPUT7 = 1; // Trip Input 7 selected as combinational ORed input to DCBH mux

EPwm1Regs.DCBHTRIPSEL.bit.TRIPINPUT8 = 1; // Trip Input 8 selected as combinational ORed input to DCBH mux

EPwm1Regs.DCBHTRIPSEL.bit.TRIPINPUT9 = 1; // Trip Input 9 selected as combinational ORed input to DCBH mux

EPwm1Regs.DCBHTRIPSEL.bit.TRIPINPUT10 = 1; // Trip Input 10 selected as combinational ORed input to DCBH mux

EPwm1Regs.DCBHTRIPSEL.bit.TRIPINPUT11 = 1; // Trip Input 11 selected as combinational ORed input to DCBH mux

EPwm1Regs.DCBHTRIPSEL.bit.TRIPINPUT12 = 1; // Trip Input 12 selected as combinational ORed input to DCBH mux

EDIS;

//----------------------Configure TZ by DC---------------------------------------------------

EALLOW;

EPwm1Regs.TZSEL.bit.DCAEVT1 = TZ_ENABLE; // Enable DCAEVT1 One-shot mode

EPwm1Regs.TZSEL.bit.DCBEVT1 = TZ_ENABLE; // Enable DCBEVT1 One-shot mode

EPwm1Regs.TZDCSEL.bit.DCAEVT1 = TZ_DCAH_HI; // DCAH = high, DCAL = don't care

EPwm1Regs.TZDCSEL.bit.DCBEVT1 = TZ_DCBH_HI; // DCBH = high, DCBL = don't care

EPwm1Regs.TZCTL.bit.TZA = TZ_NO_CHANGE; // Disable TZA

EPwm1Regs.TZCTL.bit.TZB = TZ_NO_CHANGE; // Disable TZB

EPwm1Regs.TZCLR.bit.DCAEVT1 = TZ_CLEAR; // Clear Flag for DCAEVT1 One-Shot Trip Latch

EPwm1Regs.TZCLR.bit.DCBEVT1 = TZ_CLEAR; // Clear Flag for DCBEVT1 One-Shot Trip Latch

EDIS;

//----------------------Configure Global Load---------------------------------------------------

EALLOW;

//EPwm1Regs.GLDCFG.all = 0x07FF;

EPwm1Regs.GLDCFG.bit.CMPA_CMPAHR = 1;

EPwm1Regs.GLDCFG.bit.CMPB_CMPBHR = 1;

EPwm1Regs.GLDCFG.bit.TBPRD_TBPRDHR = 1;

EPwm1Regs.GLDCFG.bit.DBCTL = 1;

EPwm1Regs.GLDCFG.bit.DBFED_DBFEDHR = 1;

EPwm1Regs.GLDCFG.bit.DBRED_DBREDHR = 1;

EPwm1Regs.GLDCTL.bit.GLDMODE = GLD_ZRO_LD;

EPwm1Regs.GLDCTL.bit.OSHTMODE = GLD_OSHT_ENABLE;

EPwm1Regs.GLDCTL.bit.GLD = GLD_GLBLDCTL;

EDIS;

EPwm1Regs.EPWMXLINK.bit.GLDCTL2LINK = LINK_EPWM1;

EPwm1Regs.EPWMXLINK.bit.TBPRDLINK = LINK_EPWM1;

EPwm1Regs.GLDCTL2.bit.OSHTLD = 1;

}

我还利用driverLib中的库函数进行了配置,结果是一样的。

以下是DEBUG调试截图:

请问关于这个配置以及现象,有什么见解吗?

注释掉这两条语句后死区模块驱动恢复正常,DBCTL通过immediate mode 加载,证实了是shadow load异常

注释掉这两条语句后死区模块驱动恢复正常,DBCTL通过immediate mode 加载,证实了是shadow load异常