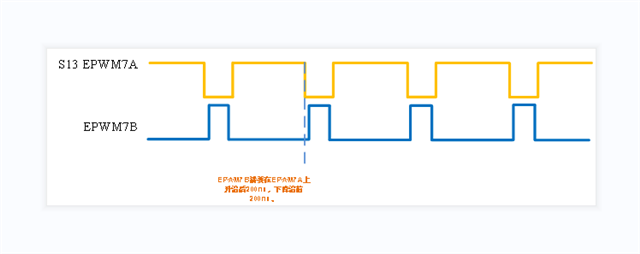

您好,因为项目需求我需要配置PWM波形 理想波形如图 但是实际的波形PEM7A的上升沿和下降沿时间我并不能修改。

但是实际的波形PEM7A的上升沿和下降沿时间我并不能修改。

代码如下:

static void ePWM7_test_Configuration(void)

{

EPwm7Regs.TBPRD = 1539; // 周期 = 2×600 TBCLK counts

EPwm7Regs.CMPA.bit.CMPA = 2; // CMPA = 400 TBCLK counts

EPwm7Regs.CMPB.bit.CMPB = 2; // CMPB = 500 TBCLK counts

EPwm7Regs.TBPHS.bit.TBPHS = 0; // 偏移量为0

EPwm7Regs.TBCTR = 0; // 清0时基计数器

EPwm7Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // 上下计数模式

EPwm7Regs.TBCTL.bit.PHSEN = TB_DISABLE; // 禁用偏移

EPwm7Regs.TBCTL.bit.PRDLD = TB_SHADOW; //影子寄存器载入模式

EPwm7Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_DISABLE;

EPwm7Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // 分频系数为1,不分频

EPwm7Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EPwm7Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;//CMPA载入为影子寄存器模式

EPwm7Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;//CMPB载入为影子寄存器模式

EPwm7Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // 计数到0时重装载CMPA

EPwm7Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO; // 计数到0时重装载CMPB

EPwm7Regs.AQCTLA.bit.CAU = AQ_SET;//向上计数到CMPA时EPWMA输出为高

EPwm7Regs.AQCTLA.bit.CAD = AQ_CLEAR;//向下计数到CMPA时EPWMA输出为低

EPwm7Regs.AQCTLB.bit.CBU = AQ_SET;//向上计数到CMPB时EPWMB输出为高

EPwm7Regs.AQCTLB.bit.CBD = AQ_CLEAR;//向下计数到CMPB时EPWMB输出为低

EPwm7Regs.TBPHS.bit.TBPHS = PWM7_PHASE_VAL;

EPwm7Regs.TBCTL.bit.PHSDIR = TB_UP; /* Count down after the synchronization event*/

EPwm7Regs.TBCTL.bit.PHSEN = TB_ENABLE; /* Enable phase loading */

EPwm7Regs.AQSFRC.bit.RLDCSF = 3; // Load immediately

EPwm7Regs.AQCSFRC.bit.CSFA = 2; //Forces a continuous low on output A

EPwm7Regs.AQCSFRC.bit.CSFB = 2; //Forces a continuous low on output B

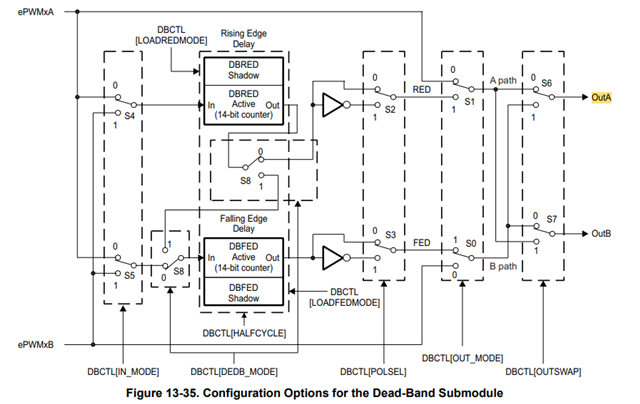

EPwm7Regs.DBCTL.bit.IN_MODE = DB_IN_A;

EPwm7Regs.DBCTL.bit.DEDB_MODE = 0U;

EPwm7Regs.DBCTL.bit.POLSEL = DB_SEL_A_B_F; // 10: Active high complementary (AHC). EPWMxB is inverted.

EPwm7Regs.DBCTL.bit.OUT_MODE = 2U;

EPwm7Regs.DBCTL.bit.OUTSWAP = 0U; /* Bit 13 controls the S6 switch and bit 12 controls the S7 switch. */

// OutA = B-path as defined by OUT-MODE bits OutB = B-path as defined by OUT-MODE bits.

EPwm7Regs.DBCTL.bit.LOADFEDMODE = 1U;

EPwm7Regs.DBCTL.bit.LOADREDMODE = 1U;

EPwm7Regs.DBCTL.bit.SHDWDBFEDMODE = 0U;

EPwm7Regs.DBCTL.bit.SHDWDBREDMODE = 0U;

EPwm7Regs.DBCTL2.bit.LOADDBCTLMODE = 1U;

EPwm7Regs.DBCTL2.bit.SHDWDBCTLMODE = 0U;

EPwm7Regs.DBRED.bit.DBRED = 0; // 0ns

EPwm7Regs.DBFED.bit.DBFED = 20U; // 300ns

EPwm7Regs.DCTRIPSEL.bit.DCAHCOMPSEL = 4; /* Zone5 To trip Trip5 */

EPwm7Regs.TZDCSEL.bit.DCAEVT2 = 1; /* Digital compare output B event 2 */

EPwm7Regs.TZSEL.bit.DCAEVT2 = 1; /* Configure DCB as CBC */

EPwm7Regs.DCTRIPSEL.bit.DCBHCOMPSEL = 4;

EPwm7Regs.TZDCSEL.bit.DCBEVT2 = 1; /* Digital compare output B event 2 */

EPwm7Regs.TZSEL.bit.DCBEVT2 = 1; /* Configure DCB as CBC */

//Configure DCB path to be filtered & async

EPwm7Regs.DCBCTL.bit.EVT2SRCSEL = 0; /* Source is DCBEVT2 Signa */

EPwm7Regs.DCBCTL.bit.EVT2FRCSYNCSEL = 0; /* 0: Source Is Synchronous Signal */

EPwm7Regs.DCACTL.bit.EVT2SRCSEL = 0; /* Source is DCBEVT2 Signa */

EPwm7Regs.DCACTL.bit.EVT2FRCSYNCSEL = 0;

EPwm7Regs.TZCTL.bit.TZA = 2; /* Force EPWMxA to a low state */

// EPwm7Regs.TZSEL.bit.CBC5 = 1;

EPwm7Regs.TZCTL.bit.TZB = 2; /* Force EPWMxA to a low state */

EPwm7Regs.TZCLR.bit.CBCPULSE = 0; /* CTR = zero pulse clears CBC trip latch. (Same as legacy designs */

SyncSocRegs.SYNCSELECT.bit.EPWM7SYNCIN = EPWM7_SYNC_IN;

}