为什么设置各EPWM载波同步之后,上下加载模式和单边加载(向上或者向下)的载波不同步?

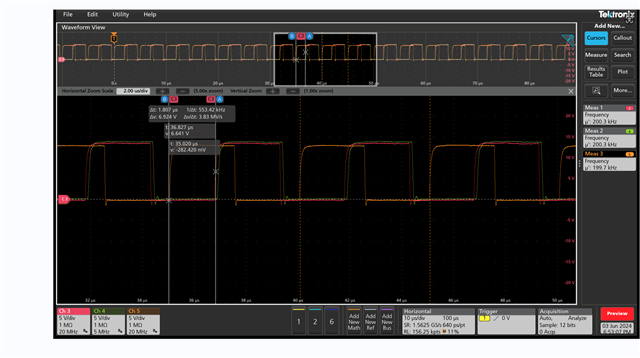

为显示载波波形,依次配置:绿 红 橙 依次为(EPWM2增减计数,ZRO高,PRD低; EPWM3增减计数,ZRO高,PRD低; EPWM1减计数,PRD高,0.5PRD低)。

目前的现象是,配置各epwm载波同步后,上下加载和上下加载的载波同步,但是单边加载和双边加载的载波之间总是存在相位差,示波器中观察到这个相位差还在从大到小、从小到大的变化。

同时,把epwm1配置成向下加载,2配置成向上加载,3配置成上下加载之后,(EPWM1减计数,PRD高,0.5PRD低; EPWM1增计数,ZRO高,0.5PRD低; EPWM3增减计数,ZRO高,PRD低),向上加载和向下加载的载波同步,但是和上下加载的不同步。

代码:

//初始化pwm,同步时钟

//

void EPWMx_Init(void)

{

EALLOW;

//使所有EPwm模块同步使用时基时钟

SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 0; //失能所有EPwm时钟

EDIS;

InitEPwm1();//具体频率进入函数修改

InitEPwm2();//具体频率进入函数修改

InitEPwm3();//具体频率进入函数修改

InitEPwm4();//具体频率进入函数修改

InitEPwm6();//具体频率进入函数修改

EALLOW;

//使所有EPwm模块同步使用时基时钟

SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 1; //使能所有EPwm时钟

EDIS;

}

//

//初始化具体pwm

//

void InitEPwm1(void)

{

EALLOW;//开启写保护

//设定时钟 TBCLK 计数模式功能

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_DOWN;// 下加载模式

EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV1; // 时钟预分频 div 1 = 60M

EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // 时钟再分频 div 1 = 60M

EPwm1Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_DISABLE; //计数为0时发出同步信号

EPwm1Regs.TBPRD = 300; // PRD寄存器 频率200k PRD = 60M/200k=300

EPwm1Regs.TBPHS.half.TBPHS = 0x0000; // 相位 0

EPwm1Regs.TBCTR = 0x0000; // 清0计数寄存器

//正常状态下使用

EPwm1Regs.TBCTL.bit.PRDLD = TB_SHADOW; //正常状态下影子寄存器模式

//设定影子寄存器

EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; // 设定CMPA为影子模式

EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW; // 设定CMPB为影子模式

EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // 设定CTR=ZERO时,装载CPMA比较值

EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO; // 设定CTR=ZERO时,装载CPMB比较值

//测试载波同步

EPwm1Regs.CMPA.half.CMPA = 150; // 设定比较值A

EPwm1Regs.CMPB = 150;

//测试载波同步

EPwm1Regs.AQCTLA.bit.PRD =AQ_SET; //CTR=PRD 时,EPwmA输出高电平

EPwm1Regs.AQCTLA.bit.CAD =AQ_CLEAR; //CTR=0时,EPwmA输出低电平

EPwm1Regs.AQCTLB.bit.PRD =AQ_SET; //CTR=PRD 时,EPwmA输出高电平

EPwm1Regs.AQCTLB.bit.CBD =AQ_CLEAR; //CTR=0时,EPwmA输出低电平

EDIS;

}

void InitEPwm2(void)

{

EALLOW;//开启写保护

//设定时钟 TBCLK 计数模式功能

EPwm2Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP;// 上加载模式

EPwm2Regs.TBCTL.bit.CLKDIV = TB_DIV1; // 时钟预分频 div 1 = 60M

EPwm2Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // 时钟再分频 div 1 = 60M

EPwm2Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_DISABLE; //计数为0时发出同步信号

EPwm2Regs.TBPRD = 300; // PRD寄存器 频率200k PRD = 60M/200k/2=150

EPwm2Regs.TBPHS.half.TBPHS = 0x0000; // 相位 0

EPwm2Regs.TBCTR = 0x0000; // 清0计数寄存器

//正常状态下使用

EPwm2Regs.TBCTL.bit.PRDLD = TB_SHADOW; //正常状态下影子寄存器模式

//设定影子寄存器

EPwm2Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; // 设定CMPA为影子模式

EPwm2Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW; // 设定CMPB为影子模式

EPwm2Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // 设定CTR=ZERO时,装载CPMA比较值

EPwm2Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO; // 设定CTR=ZERO时,装载CPMB比较值

//设定初始化比较值

EPwm2Regs.CMPA.half.CMPA = 150; // 设定比较值A

EPwm2Regs.CMPB = 150;

//测试载波同步

//测试载波同步

EPwm2Regs.AQCTLA.bit.ZRO =AQ_SET; //CTR=PRD 时,EPwmA输出高电平

EPwm2Regs.AQCTLA.bit.CAU =AQ_CLEAR; //CTR=0时,EPwmA输出低电平

EPwm2Regs.AQCTLB.bit.ZRO =AQ_SET; //CTR=PRD 时,EPwmA输出高电平

EPwm2Regs.AQCTLB.bit.CBU =AQ_CLEAR; //CTR=0时,EPwmA输出低电平

EDIS;

}

void InitEPwm3(void)

{

EALLOW;//开启写保护

//设定时钟 TBCLK 计数模式功能

EPwm3Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN;// 上下加载模式

EPwm3Regs.TBCTL.bit.CLKDIV = TB_DIV1; // 时钟预分频 div 1 = 60M

EPwm3Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // 时钟再分频 div 1 = 60M

EPwm3Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_DISABLE; //计数为0时发出同步信号

EPwm3Regs.TBPRD = 150; // PRD寄存器 频率200k PRD = 60M/200k/2=150

EPwm3Regs.TBPHS.half.TBPHS = 0x0000; // 相位 0

EPwm3Regs.TBCTR = 0x0000; // 清0计数寄存器

//正常状态下使用

EPwm3Regs.TBCTL.bit.PRDLD = TB_SHADOW; //正常状态下影子寄存器模式

//测试运行时间用

//EPwm3Regs.TBCTL.bit.PRDLD = TB_IMMEDIATE; //测试运行时间使用连续模式

//设定影子寄存器

EPwm3Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; // 设定CMPA为影子模式

EPwm3Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW; // 设定CMPB为影子模式

EPwm3Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // 设定CTR=ZERO时,装载CPMA比较值

EPwm3Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO; // 设定CTR=ZERO时,装载CPMB比较值

//设定初始化比较值

EPwm3Regs.CMPA.half.CMPA = 150; // 设定比较值A

EPwm3Regs.CMPB =150; // 设定比较值B

//设定初始AQCTL动作功能

EPwm3Regs.AQCTLA.bit.CAU =0;//AQ_SET; //CTR=CMPA增计数时,EPwmA输出高电平

EPwm3Regs.AQCTLA.bit.CAD =0;//AQ_CLEAR; //CTR=CMPA减计数时,EPwmA输出低电平

EPwm3Regs.AQCTLB.bit.CBU =0;//AQ_SET; //CTR=CMPBA增计数时,EPwmB输出高电平

EPwm3Regs.AQCTLB.bit.CBD =0;//AQ_CLEAR; //CTR=CMPB减计数时,EPwmB输出低电平

//测试载波同步

EPwm3Regs.AQCTLA.bit.PRD =AQ_CLEAR; //CTR=PRD 时,EPwmA输出高电平

EPwm3Regs.AQCTLA.bit.ZRO =AQ_SET; //CTR=0时,EPwmA输出低电平

EPwm3Regs.AQCTLB.bit.PRD =AQ_CLEAR; //CTR=PRD 时,EPwmA输出高电平

EPwm3Regs.AQCTLB.bit.ZRO =AQ_SET; //CTR=0时,EPwmA输出低电平

//开启CPU第一组中断并使能第3组中断的第3个小中断,即EPwm3->INT3.3

IER |=M_INT3; //使能CPU中断3(INT3)

PieCtrlRegs.PIEIER3.bit.INTx3=1;//使能PIE-INT3.3

EINT;//使能总中断

ERTM;//当使用仿真器调试时可开启 DEBUG 中断,即使用 ERTM 语句

EDIS;

}