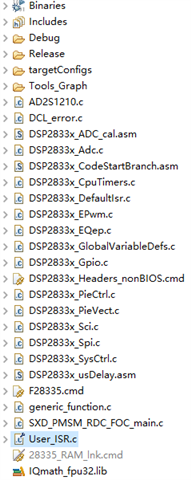

我使用非线性PID设计了一台永磁同步电机的FOC算法,工程如下:

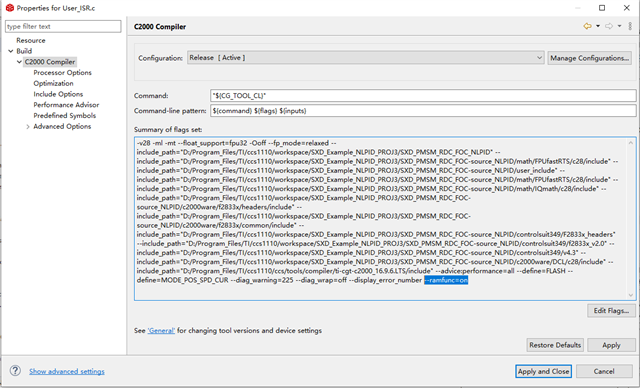

我将需要下载至flash随后需要搬移到ram中运行的函数都设计在User_ISR.c中,并为User_ISR.c文件添加了“--ramfunc=on”编译tag,如下图所示:

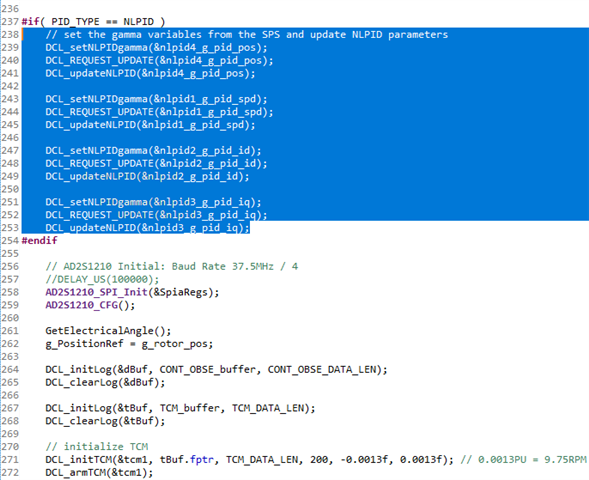

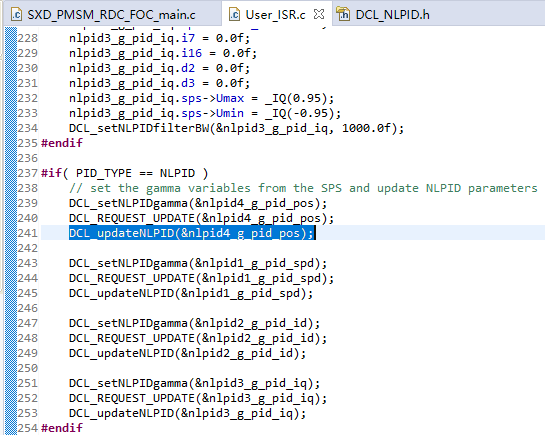

在该文件中,我调用了非线性PID参数配置函数

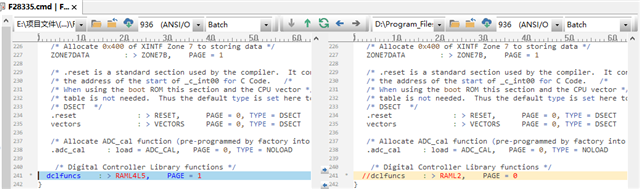

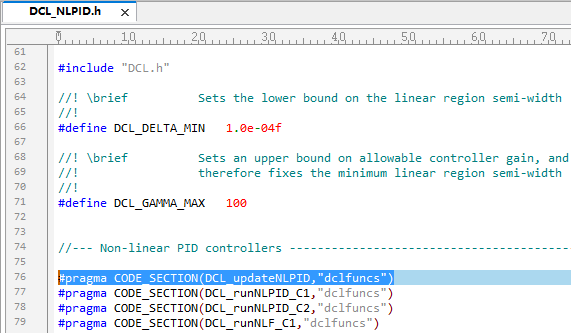

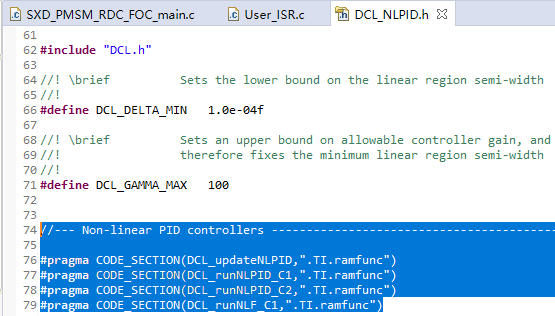

DCL_NLPID.h文件中的原本的code section定义如下

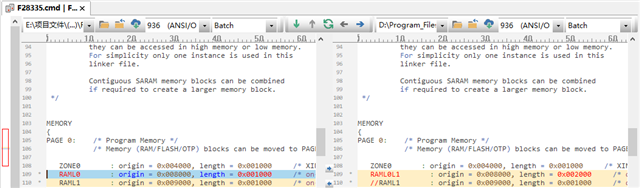

在cmd文件中再将dclfuncs段分配到相应的ram空间,我的F28335.cmd文件内容如下:

/*

// TI File $Revision: /main/10 $

// Checkin $Date: July 9, 2008 13:43:56 $

//###########################################################################

//

// FILE: F28335.cmd

//

// TITLE: Linker Command File For F28335 Device

//

//###########################################################################

// $TI Release: F2833x Support Library v2.02.00.00 $

// $Release Date: Fri Feb 12 19:15:21 IST 2021 $

// $Copyright:

// Copyright (C) 2009-2021 Texas Instruments Incorporated - http://www.ti.com/

//

// Redistribution and use in source and binary forms, with or without

// modification, are permitted provided that the following conditions

// are met:

//

// Redistributions of source code must retain the above copyright

// notice, this list of conditions and the following disclaimer.

//

// Redistributions in binary form must reproduce the above copyright

// notice, this list of conditions and the following disclaimer in the

// documentation and/or other materials provided with the

// distribution.

//

// Neither the name of Texas Instruments Incorporated nor the names of

// its contributors may be used to endorse or promote products derived

// from this software without specific prior written permission.

//

// THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

// "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

// LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

// A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT

// OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL,

// SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT

// LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

// DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

// THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

// (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

// OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

// $

//###########################################################################

*/

/* ======================================================

// For Code Composer Studio V2.2 and later

// ---------------------------------------

// In addition to this memory linker command file,

// add the header linker command file directly to the project.

// The header linker command file is required to link the

// peripheral structures to the proper locations within

// the memory map.

//

// The header linker files are found in <base>\headers\cmd

//

// For BIOS applications add: DSP2833x_Headers_BIOS.cmd

// For nonBIOS applications add: DSP2833x_Headers_nonBIOS.cmd

========================================================= */

/* ======================================================

// For Code Composer Studio prior to V2.2

// --------------------------------------

// 1) Use one of the following -l statements to include the

// header linker command file in the project. The header linker

// file is required to link the peripheral structures to the proper

// locations within the memory map */

/* Uncomment this line to include file only for non-BIOS applications */

/* -l DSP2833x_Headers_nonBIOS.cmd */

/* Uncomment this line to include file only for BIOS applications */

/* -l DSP2833x_Headers_BIOS.cmd */

/* 2) In your project add the path to <base>\headers\cmd to the

library search path under project->build options, linker tab,

library search path (-i).

/*========================================================= */

/* Define the memory block start/length for the F28335

PAGE 0 will be used to organize program sections

PAGE 1 will be used to organize data sections

Notes:

Memory blocks on F28335 are uniform (ie same

physical memory) in both PAGE 0 and PAGE 1.

That is the same memory region should not be

defined for both PAGE 0 and PAGE 1.

Doing so will result in corruption of program

and/or data.

L0/L1/L2 and L3 memory blocks are mirrored - that is

they can be accessed in high memory or low memory.

For simplicity only one instance is used in this

linker file.

Contiguous SARAM memory blocks can be combined

if required to create a larger memory block.

*/

MEMORY

{

PAGE 0: /* Program Memory */

/* Memory (RAM/FLASH/OTP) blocks can be moved to PAGE1 for data allocation */

ZONE0 : origin = 0x004000, length = 0x001000 /* XINTF zone 0 */

RAML0 : origin = 0x008000, length = 0x001000 /* on-chip RAM block L0 */

RAML1 : origin = 0x009000, length = 0x001000 /* on-chip RAM block L1 */

RAML2 : origin = 0x00A000, length = 0x001000 /* on-chip RAM block L2 */

RAML3 : origin = 0x00B000, length = 0x001000 /* on-chip RAM block L3 */

ZONE6 : origin = 0x0100000, length = 0x100000 /* XINTF zone 6 */

ZONE7A : origin = 0x0200000, length = 0x00FC00 /* XINTF zone 7 - program space */

FLASHH : origin = 0x300000, length = 0x008000 /* on-chip FLASH */

FLASHG : origin = 0x308000, length = 0x008000 /* on-chip FLASH */

FLASHF : origin = 0x310000, length = 0x008000 /* on-chip FLASH */

FLASHE : origin = 0x318000, length = 0x008000 /* on-chip FLASH */

FLASHD : origin = 0x320000, length = 0x008000 /* on-chip FLASH */

FLASHC : origin = 0x328000, length = 0x008000 /* on-chip FLASH */

FLASHA : origin = 0x338000, length = 0x007F80 /* on-chip FLASH */

CSM_RSVD : origin = 0x33FF80, length = 0x000076 /* Part of FLASHA. Program with all 0x0000 when CSM is in use. */

BEGIN : origin = 0x33FFF6, length = 0x000002 /* Part of FLASHA. Used for "boot to Flash" bootloader mode. */

CSM_PWL : origin = 0x33FFF8, length = 0x000008 /* Part of FLASHA. CSM password locations in FLASHA */

OTP : origin = 0x380400, length = 0x000400 /* on-chip OTP */

ADC_CAL : origin = 0x380080, length = 0x000009 /* ADC_cal function in Reserved memory */

IQTABLES : origin = 0x3FE000, length = 0x000b50 /* IQ Math Tables in Boot ROM */

IQTABLES2 : origin = 0x3FEB50, length = 0x00008c /* IQ Math Tables in Boot ROM */

FPUTABLES : origin = 0x3FEBDC, length = 0x0006A0 /* FPU Tables in Boot ROM */

ROM : origin = 0x3FF27C, length = 0x000D44 /* Boot ROM */

RESET : origin = 0x3FFFC0, length = 0x000002 /* part of boot ROM */

VECTORS : origin = 0x3FFFC2, length = 0x00003E /* part of boot ROM */

PAGE 1 : /* Data Memory */

/* Memory (RAM/FLASH/OTP) blocks can be moved to PAGE0 for program allocation */

/* Registers remain on PAGE1 */

BOOT_RSVD : origin = 0x000000, length = 0x000050 /* Part of M0, BOOT rom will use this for stack */

RAMM0 : origin = 0x000050, length = 0x0003B0 /* on-chip RAM block M0 */

RAMM1 : origin = 0x000400, length = 0x000400 /* on-chip RAM block M1 */

RAML4L5 : origin = 0x00C000, length = 0x002000 /* on-chip RAM block L1 */

//RAML5 : origin = 0x00D000, length = 0x001000 /* on-chip RAM block L1 */

RAML6 : origin = 0x00E000, length = 0x001000 /* on-chip RAM block L1 */

RAML7 : origin = 0x00F000, length = 0x001000 /* on-chip RAM block L1 */

ZONE7B : origin = 0x20FC00, length = 0x000400 /* XINTF zone 7 - data space */

FLASHB : origin = 0x330000, length = 0x008000 /* on-chip FLASH */

}

/* Allocate sections to memory blocks.

Note:

codestart user defined section in DSP28_CodeStartBranch.asm used to redirect code

execution when booting to flash

ramfuncs user defined section to store functions that will be copied from Flash into RAM

*/

SECTIONS

{

/* Allocate program areas: */

.cinit : > FLASHA PAGE = 0

.pinit : > FLASHA, PAGE = 0

.text : > FLASHA PAGE = 0

codestart : > BEGIN PAGE = 0

#ifdef __TI_COMPILER_VERSION__

#if __TI_COMPILER_VERSION__ >= 15009000

.TI.ramfunc : {} LOAD = FLASHD,

RUN = RAML0,

LOAD_START(_RamfuncsLoadStart),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

LOAD_SIZE(_RamfuncsLoadSize),

PAGE = 0

#else

ramfuncs : LOAD = FLASHD,

RUN = RAML0,

LOAD_START(_RamfuncsLoadStart),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

LOAD_SIZE(_RamfuncsLoadSize),

PAGE = 0

#endif

#endif

csmpasswds : > CSM_PWL PAGE = 0

csm_rsvd : > CSM_RSVD PAGE = 0

/* Allocate uninitalized data sections: */

.stack : > RAMM1 PAGE = 1

.ebss : > RAML4L5 PAGE = 1

.esysmem : > RAMM1 PAGE = 1

/* Initalized sections go in Flash */

/* For SDFlash to program these, they must be allocated to page 0 */

.econst : > FLASHA PAGE = 0

.switch : > FLASHA PAGE = 0

/* Allocate IQ math areas: */

IQmath : > FLASHC PAGE = 0 /* Math Code */

IQmathTables : > IQTABLES, PAGE = 0, TYPE = NOLOAD

/* Uncomment the section below if calling the IQNexp() or IQexp()

functions from the IQMath.lib library in order to utilize the

relevant IQ Math table in Boot ROM (This saves space and Boot ROM

is 1 wait-state). If this section is not uncommented, IQmathTables2

will be loaded into other memory (SARAM, Flash, etc.) and will take

up space, but 0 wait-state is possible.

*/

/*

IQmathTables2 : > IQTABLES2, PAGE = 0, TYPE = NOLOAD

{

IQmath.lib<IQNexpTable.obj> (IQmathTablesRam)

}

*/

FPUmathTables : > RAML1, PAGE = 0

/* Allocate DMA-accessible RAM sections: */

DMARAML4 : > RAML4L5, PAGE = 1

DMARAML5 : > RAML4L5, PAGE = 1

DMARAML6 : > RAML6, PAGE = 1

DMARAML7 : > RAML7, PAGE = 1

/* Allocate 0x400 of XINTF Zone 7 to storing data */

ZONE7DATA : > ZONE7B, PAGE = 1

/* .reset is a standard section used by the compiler. It contains the */

/* the address of the start of _c_int00 for C Code. /*

/* When using the boot ROM this section and the CPU vector */

/* table is not needed. Thus the default type is set here to */

/* DSECT */

.reset : > RESET, PAGE = 0, TYPE = DSECT

vectors : > VECTORS PAGE = 0, TYPE = DSECT

/* Allocate ADC_cal function (pre-programmed by factory into TI reserved memory) */

.adc_cal : load = ADC_CAL, PAGE = 0, TYPE = NOLOAD

/* Digital Controller Library functions */

dclfuncs : > RAML4L5, PAGE = 1

}

/*

//===========================================================================

// End of file.

//===========================================================================

*/

即将dclfuncs段分配至RAML4L5

按照上述配置,我在以下情况下运行代码都是正常的:

1.通过仿真器烧录,并在CCS环境下运行

2.通过仿真器烧录,并在CCS环境下运行;随后关闭CCS环境,按下开发板上的28335硬件复位按键,之后发送指令,运行正常

但是如果将电路板断电,再上电,程序无法运行,通过脱离仿真器、利用开发板上点亮指示灯的方式,确定代码跑飞的位置如下:

如上图所示,在241行前增加点亮指示灯代码,是可以正常点亮指示灯的,在241行后,增加熄灭指示灯代码,是无法将指示灯熄灭的,由此判断,程序在241行跑飞。

最终我做了如下修改,使得非线性PID工程可以在断电重启的情况下正常运行:

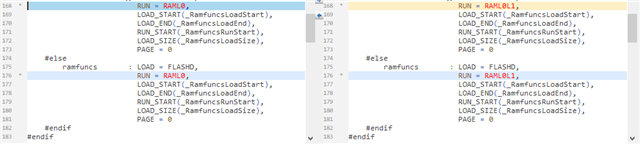

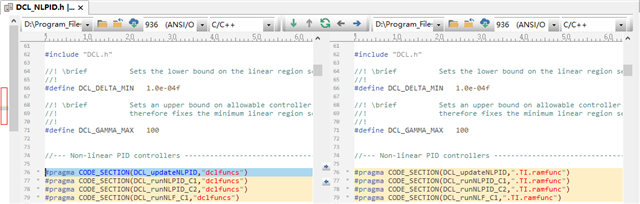

如上图所示,我使用的编译器版本是16.9.6,所以我将code section由原本的“dclfuncs”修改为“.TI.ramfunc”,并将cmd文件中的dclfuncs段分配语句注释掉,同时将RAML0、RAML1整合在一起使用,最终的CMD文件如下所示:

/*

// TI File $Revision: /main/10 $

// Checkin $Date: July 9, 2008 13:43:56 $

//###########################################################################

//

// FILE: F28335.cmd

//

// TITLE: Linker Command File For F28335 Device

//

//###########################################################################

// $TI Release: F2833x Support Library v2.02.00.00 $

// $Release Date: Fri Feb 12 19:15:21 IST 2021 $

// $Copyright:

// Copyright (C) 2009-2021 Texas Instruments Incorporated - http://www.ti.com/

//

// Redistribution and use in source and binary forms, with or without

// modification, are permitted provided that the following conditions

// are met:

//

// Redistributions of source code must retain the above copyright

// notice, this list of conditions and the following disclaimer.

//

// Redistributions in binary form must reproduce the above copyright

// notice, this list of conditions and the following disclaimer in the

// documentation and/or other materials provided with the

// distribution.

//

// Neither the name of Texas Instruments Incorporated nor the names of

// its contributors may be used to endorse or promote products derived

// from this software without specific prior written permission.

//

// THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

// "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

// LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

// A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT

// OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL,

// SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT

// LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

// DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

// THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

// (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

// OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

// $

//###########################################################################

*/

/* ======================================================

// For Code Composer Studio V2.2 and later

// ---------------------------------------

// In addition to this memory linker command file,

// add the header linker command file directly to the project.

// The header linker command file is required to link the

// peripheral structures to the proper locations within

// the memory map.

//

// The header linker files are found in <base>\headers\cmd

//

// For BIOS applications add: DSP2833x_Headers_BIOS.cmd

// For nonBIOS applications add: DSP2833x_Headers_nonBIOS.cmd

========================================================= */

/* ======================================================

// For Code Composer Studio prior to V2.2

// --------------------------------------

// 1) Use one of the following -l statements to include the

// header linker command file in the project. The header linker

// file is required to link the peripheral structures to the proper

// locations within the memory map */

/* Uncomment this line to include file only for non-BIOS applications */

/* -l DSP2833x_Headers_nonBIOS.cmd */

/* Uncomment this line to include file only for BIOS applications */

/* -l DSP2833x_Headers_BIOS.cmd */

/* 2) In your project add the path to <base>\headers\cmd to the

library search path under project->build options, linker tab,

library search path (-i).

/*========================================================= */

/* Define the memory block start/length for the F28335

PAGE 0 will be used to organize program sections

PAGE 1 will be used to organize data sections

Notes:

Memory blocks on F28335 are uniform (ie same

physical memory) in both PAGE 0 and PAGE 1.

That is the same memory region should not be

defined for both PAGE 0 and PAGE 1.

Doing so will result in corruption of program

and/or data.

L0/L1/L2 and L3 memory blocks are mirrored - that is

they can be accessed in high memory or low memory.

For simplicity only one instance is used in this

linker file.

Contiguous SARAM memory blocks can be combined

if required to create a larger memory block.

*/

MEMORY

{

PAGE 0: /* Program Memory */

/* Memory (RAM/FLASH/OTP) blocks can be moved to PAGE1 for data allocation */

ZONE0 : origin = 0x004000, length = 0x001000 /* XINTF zone 0 */

RAML0L1 : origin = 0x008000, length = 0x002000 /* on-chip RAM block L0 */

//RAML1 : origin = 0x009000, length = 0x001000 /* on-chip RAM block L1 */

RAML2 : origin = 0x00A000, length = 0x001000 /* on-chip RAM block L2 */

RAML3 : origin = 0x00B000, length = 0x001000 /* on-chip RAM block L3 */

ZONE6 : origin = 0x0100000, length = 0x100000 /* XINTF zone 6 */

ZONE7A : origin = 0x0200000, length = 0x00FC00 /* XINTF zone 7 - program space */

FLASHH : origin = 0x300000, length = 0x008000 /* on-chip FLASH */

FLASHG : origin = 0x308000, length = 0x008000 /* on-chip FLASH */

FLASHF : origin = 0x310000, length = 0x008000 /* on-chip FLASH */

FLASHE : origin = 0x318000, length = 0x008000 /* on-chip FLASH */

FLASHD : origin = 0x320000, length = 0x008000 /* on-chip FLASH */

FLASHC : origin = 0x328000, length = 0x008000 /* on-chip FLASH */

FLASHA : origin = 0x338000, length = 0x007F80 /* on-chip FLASH */

CSM_RSVD : origin = 0x33FF80, length = 0x000076 /* Part of FLASHA. Program with all 0x0000 when CSM is in use. */

BEGIN : origin = 0x33FFF6, length = 0x000002 /* Part of FLASHA. Used for "boot to Flash" bootloader mode. */

CSM_PWL : origin = 0x33FFF8, length = 0x000008 /* Part of FLASHA. CSM password locations in FLASHA */

OTP : origin = 0x380400, length = 0x000400 /* on-chip OTP */

ADC_CAL : origin = 0x380080, length = 0x000009 /* ADC_cal function in Reserved memory */

IQTABLES : origin = 0x3FE000, length = 0x000b50 /* IQ Math Tables in Boot ROM */

IQTABLES2 : origin = 0x3FEB50, length = 0x00008c /* IQ Math Tables in Boot ROM */

FPUTABLES : origin = 0x3FEBDC, length = 0x0006A0 /* FPU Tables in Boot ROM */

ROM : origin = 0x3FF27C, length = 0x000D44 /* Boot ROM */

RESET : origin = 0x3FFFC0, length = 0x000002 /* part of boot ROM */

VECTORS : origin = 0x3FFFC2, length = 0x00003E /* part of boot ROM */

PAGE 1 : /* Data Memory */

/* Memory (RAM/FLASH/OTP) blocks can be moved to PAGE0 for program allocation */

/* Registers remain on PAGE1 */

BOOT_RSVD : origin = 0x000000, length = 0x000050 /* Part of M0, BOOT rom will use this for stack */

RAMM0 : origin = 0x000050, length = 0x0003B0 /* on-chip RAM block M0 */

RAMM1 : origin = 0x000400, length = 0x000400 /* on-chip RAM block M1 */

RAML4L5 : origin = 0x00C000, length = 0x002000 /* on-chip RAM block L1 */

//RAML5 : origin = 0x00D000, length = 0x001000 /* on-chip RAM block L1 */

RAML6 : origin = 0x00E000, length = 0x001000 /* on-chip RAM block L1 */

RAML7 : origin = 0x00F000, length = 0x001000 /* on-chip RAM block L1 */

ZONE7B : origin = 0x20FC00, length = 0x000400 /* XINTF zone 7 - data space */

FLASHB : origin = 0x330000, length = 0x008000 /* on-chip FLASH */

}

/* Allocate sections to memory blocks.

Note:

codestart user defined section in DSP28_CodeStartBranch.asm used to redirect code

execution when booting to flash

ramfuncs user defined section to store functions that will be copied from Flash into RAM

*/

SECTIONS

{

/* Allocate program areas: */

.cinit : > FLASHA PAGE = 0

.pinit : > FLASHA, PAGE = 0

.text : > FLASHA PAGE = 0

codestart : > BEGIN PAGE = 0

#ifdef __TI_COMPILER_VERSION__

#if __TI_COMPILER_VERSION__ >= 15009000

.TI.ramfunc : {} LOAD = FLASHD,

RUN = RAML0L1,

LOAD_START(_RamfuncsLoadStart),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

LOAD_SIZE(_RamfuncsLoadSize),

PAGE = 0

#else

ramfuncs : LOAD = FLASHD,

RUN = RAML0L1,

LOAD_START(_RamfuncsLoadStart),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

LOAD_SIZE(_RamfuncsLoadSize),

PAGE = 0

#endif

#endif

csmpasswds : > CSM_PWL PAGE = 0

csm_rsvd : > CSM_RSVD PAGE = 0

/* Allocate uninitalized data sections: */

.stack : > RAMM1 PAGE = 1

.ebss : > RAML4L5 PAGE = 1

.esysmem : > RAMM1 PAGE = 1

/* Initalized sections go in Flash */

/* For SDFlash to program these, they must be allocated to page 0 */

.econst : > FLASHA PAGE = 0

.switch : > FLASHA PAGE = 0

/* Allocate IQ math areas: */

IQmath : > FLASHC PAGE = 0 /* Math Code */

IQmathTables : > IQTABLES, PAGE = 0, TYPE = NOLOAD

/* Uncomment the section below if calling the IQNexp() or IQexp()

functions from the IQMath.lib library in order to utilize the

relevant IQ Math table in Boot ROM (This saves space and Boot ROM

is 1 wait-state). If this section is not uncommented, IQmathTables2

will be loaded into other memory (SARAM, Flash, etc.) and will take

up space, but 0 wait-state is possible.

*/

/*

IQmathTables2 : > IQTABLES2, PAGE = 0, TYPE = NOLOAD

{

IQmath.lib<IQNexpTable.obj> (IQmathTablesRam)

}

*/

FPUmathTables : > RAML0L1, PAGE = 0

/* Allocate DMA-accessible RAM sections: */

DMARAML4 : > RAML4L5, PAGE = 1

DMARAML5 : > RAML4L5, PAGE = 1

DMARAML6 : > RAML6, PAGE = 1

DMARAML7 : > RAML7, PAGE = 1

/* Allocate 0x400 of XINTF Zone 7 to storing data */

ZONE7DATA : > ZONE7B, PAGE = 1

/* .reset is a standard section used by the compiler. It contains the */

/* the address of the start of _c_int00 for C Code. /*

/* When using the boot ROM this section and the CPU vector */

/* table is not needed. Thus the default type is set here to */

/* DSECT */

.reset : > RESET, PAGE = 0, TYPE = DSECT

vectors : > VECTORS PAGE = 0, TYPE = DSECT

/* Allocate ADC_cal function (pre-programmed by factory into TI reserved memory) */

.adc_cal : load = ADC_CAL, PAGE = 0, TYPE = NOLOAD

/* Digital Controller Library functions */

//dclfuncs : > RAML2, PAGE = 0

}

/*

//===========================================================================

// End of file.

//===========================================================================

*/

我不明白为什么这样做可以使工程断电重启后正常运行。

1.DCL_NLPID.h文件修改内容(右侧为修改后的文件):

2.F28335.cmd文件修改内容(右侧为修改后的文件):