280049的TZ模块能CBC模式下,事件A和B发生时分别封epwmA和epwmB,而不是一起封.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

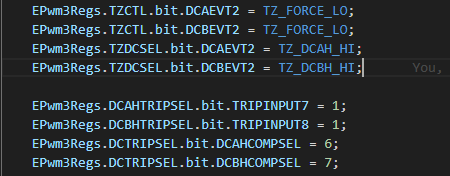

是不是CBC1事件也发生了,看着DCAEVT2和DCBEVT2的配置没啥问题。

设置应该是错的,但可以实现我要的结果,在实际实验中确实可以双向逐波限流,无法理解

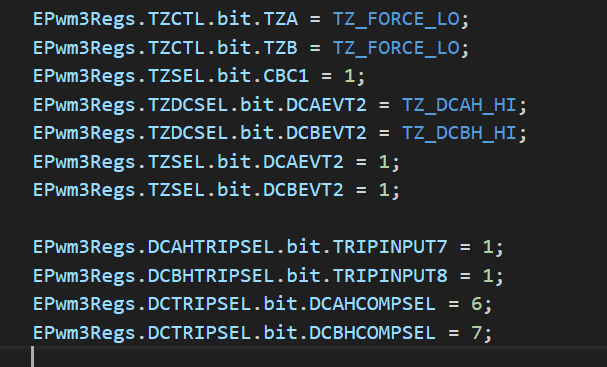

正确的寄存器设置应该是这样的

直接通过事件A2/B2去封波,cmpss不能设置成锁存

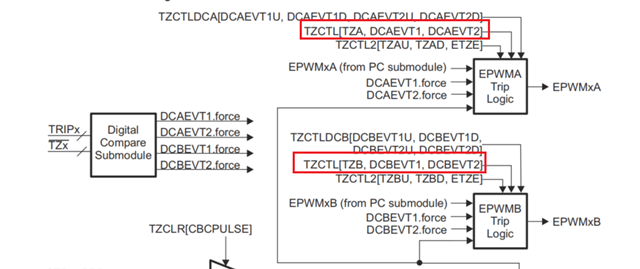

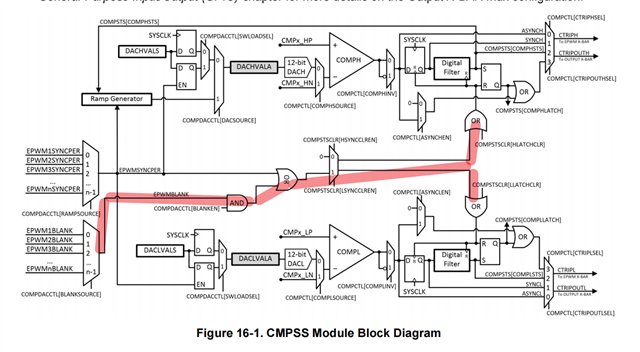

是的,要想分别对PWMA和PWMB进行封波,就既不能走CBC的路径,也不能走OSHT的路径,因为这两条路径最后动作都是合并在一起的。只能选择DCAEVT1.force和DCBEVT1.force直接控制PWMA和PWMB,而且DCAEVT1.force和DCBEVT1.force这两给信号是不锁存的。这样可能会带来一个问题:就是在一个周期内,如果DCAEVT1.force的状态为 0->1->0->1->0....这样不停变化的话,PWMA也会随之开->关->开->关->开.....

不知我的理解是否正确。

TZA和TZB也可以实现EPWMA/B的封波,之前的配置为何不行呢,是不是还有其他地方也改了。

我是通过cmpss模块去产生事件,感觉可以通过cmpss的锁存去解决这个问题,不知道我的想法是否可行

可以,那岂不是DCAEVT2.force和DCBEVT2.force为高时会封波,一旦为低时又会继续发波,没有周期清除这些概念了吧。

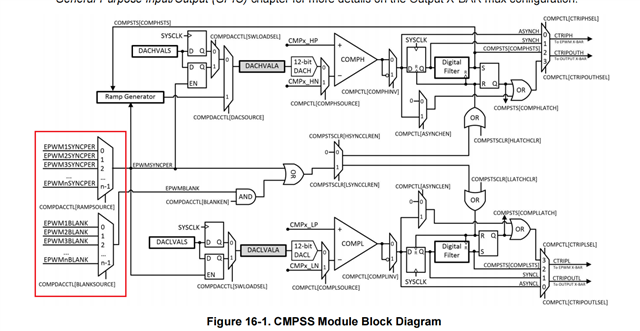

嗯,这个方式是可行的。CMSS输出CTRIH(to epwm x-bar)选择带锁存的CMPSTS,CMPSTS通过EPWMSYNCPER进行周期清除。

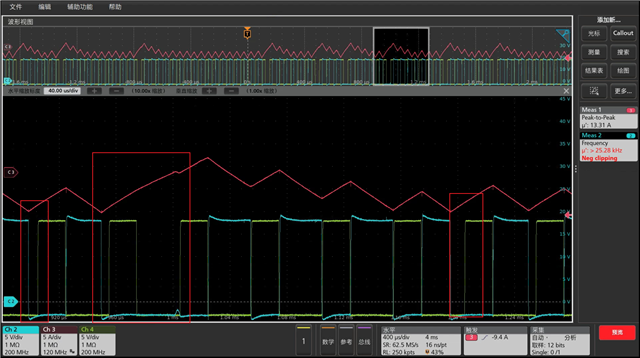

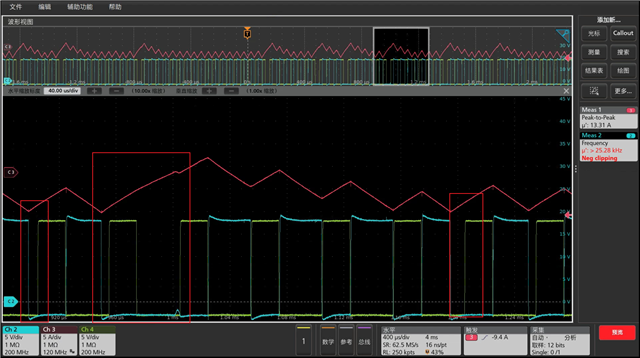

是的,这个方法是可行的。请教一下,现在出现了一个新的问题,无论我的CMPSTS清除锁存时刻选在EPWM周期的哪个时刻,偶尔会出现封波多封了一个周期的现象,如图所示

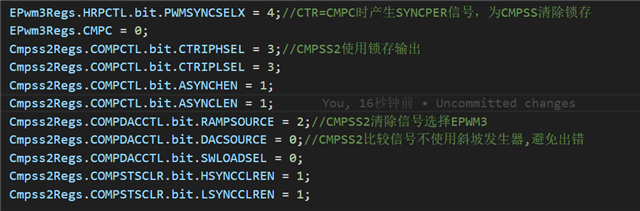

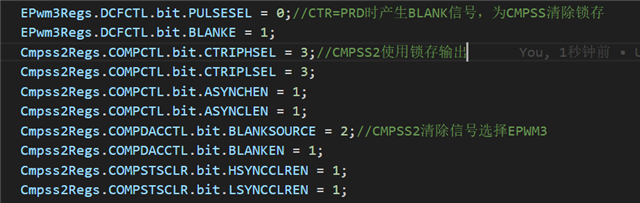

这是我的寄存器设置

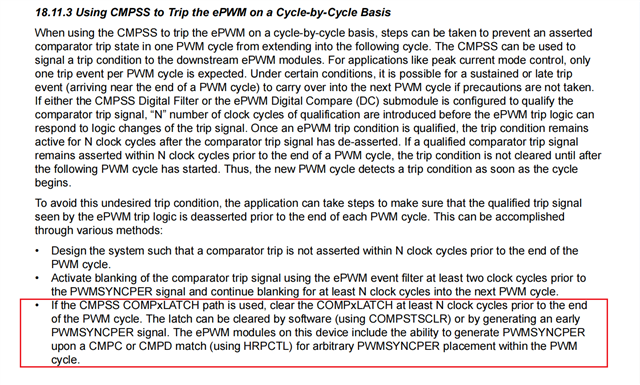

我看手册上是说“需要在EPWM周期结束前至少N个时钟周期清除cmpss锁存”,这个N是多少呢?它与什么参数相关?

波形里的锯齿波是什么信号?

Cmpss2 H/L的信号幅值显示吗?和PWM的开关位置是否对应?

锯齿波是电流信号,当电流小于一定数值后,蓝色波形(驱动)被封锁。但在第二个红色框内,蓝色波形多消失了一个周期。cmpss2的H/L信号并未引出

看手册上的描述意思是,不管CBC还是CMPSS的锁存信号,都需要再PWM的周期结束前N个周期执行清楚操作才能避免这个锁存信号被带入下个周期。这里还隐含了一个条件,就是当执行清楚操作时,触发锁存信号的外部条件已经消失(对应你的实际条件就是电流要大于设定值),否则就算执行了清楚操作,马上又锁存上了。所以我觉得需要按手册上说的那样,把消隐窗口( BLANKWDW)打开,让它处于PWM周期的前后一定宽度。然后周期清锁存还是处于周期的位置。这样可以控制清锁存的操作和锁存信号前后距离。你可以试试看行不行。

这个“N”我没有找到具体的说明,但是我估计是滤波的的原因,因为我们对信号进行滤波后,实际的效果就是会带来一定的滞后效应;所以锁存信号会发生在真实信号之后的一定时间,如果超过了清除缓存的位置,那么清除操作就不能起作用了。不同的滤波参数对应的N就不一样。

是的,我觉得你是正确的,应该是清除锁存后,立马又锁存上了,锁存信息被带入到下一个EPWM周期了。我现在通过CMPSS的BLANK通道去清除锁存,已经没有这个问题了

说实话,我还不太理解原理,我还在查阅手册,这是我的寄存器设置

您好

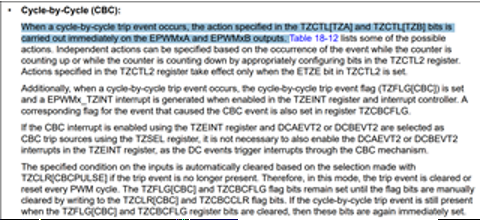

遗憾的是、对于发生的任何跳闸事件(CBC 或 OST)、TZA 和 TSB 的配置将应用于两个通道(A 和 B)、如 TRM 所述(请参阅下文)、因为跳闸源未区分(它们进行"或"运算):

一个可能的替代方案是可以选择使用数字比较子模块的.force 信号。 为此、您需要将 DCxEVTY.FORCE 直接连接到通道 A 或通道 B 跳闸逻辑、以便会影响想要的独立通道;然而、输出条件只会持续存在。