This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好

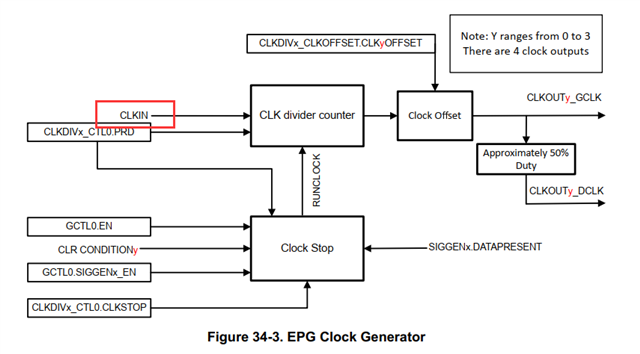

根据datasheet来说明,CLKIN的时钟来自PERx.SYSCLK。PERx.SYSCLK来自CPU时钟

3.7.3.3 CPU Subsystem Clock (SYSCLK and PERx.SYSCLK) Each CPU provides a clock (CPU1.SYSCLK and CPU2.SYSCLK) to the CLA, DMA, and most owned peripherals. This clock is identical to PLLSYSCLK, but is gated when the CPU enters STANDBY mode. Each peripheral clock can be connected to either CPU1.SYSCLK or CPU2.SYSCLK. This selection is made by CPU1 using the CPUSELx registers. Each peripheral clock also has an independent clock gating that is controlled by the CPU PCLKCRx registers. By default, the ePWM and EMIF1 clocks each have an additional /2 divider, which is required to support CPU frequencies over 100MHz. At slower CPU frequencies, these dividers can be disabled using the PERCLKDIVSEL register.

根据以上说明应该不能从外部时钟获得。