Other Parts Discussed in Thread: TMS320F2809

您好,我最近要完成fpga和dsp芯片的spi通信,因为之前对dsp没有接触,所以现在正在看它的数据手册,我用的芯片是TMS320f2809,在看的过程中对它的spi通信时序图地方有些不明白:

(1)从机选择信号cs无效时,spi时钟此时应处于什么状态?也就是说是在cs信号有效时开始sck时钟还是说sck时钟不管cs信号是否有效都一直在输出时钟信号?

(2)该芯片能否连续发送数据,即cs信号能否一直处于低电平的有效状态,还是说每发送一次指定位数的数据,需要把cs信号拉高一段时间?

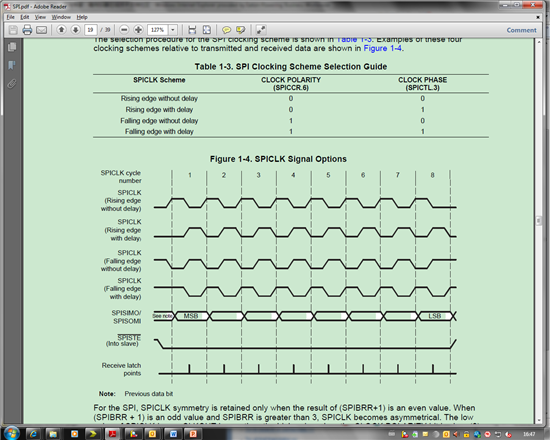

(3)在介绍spi的时候,当时钟的极性cpol=0,时钟相位cpha=0时,数据手册给的是在上升沿发送数据,下降沿接收数据,

(手册是TMS320x280x, 2801x, 2804x Serial Peripheral Interface Reference Guide,

Literature Number: SPRUG72 February 2009)

但是我在看对于spi通信协议的介绍的时候如果处于这种情况是上升沿接收数据,下降沿发送数据,和芯片介绍正好相反,这是怎么回事?还是说spi的通信协议根据不同的芯片其规定也是不同的吗?

因为之前对dsp从来没有接触过,所以很多问题看了手册还是不太明白,谢谢!