1.clllc,做同步整流;

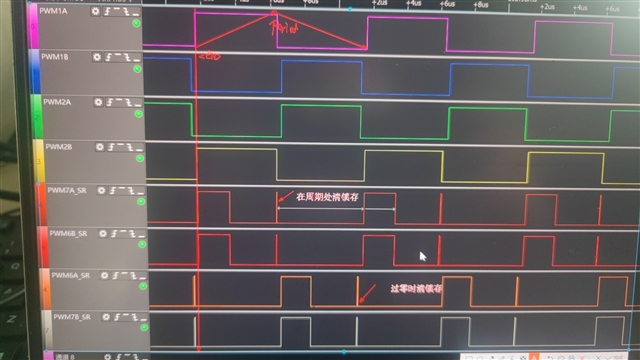

pwm1、pwm2为原边驱动,pwm6、pwm7为副边同步整流驱动(4路驱动配置均为计数模式updown,1A 1B上下管互补),aqctla选择zero/period置高置低输出电平;

2.使用谐振电流送入比较器(高低两个比较器)后,比较器输出通过xbar配置ctriph到trip4上,ctripl到trip5上;pwm6/7的DCALCOMPSEL/DCBLCOMPSEL选择trip4/5。

- 3.问题现象,当比较器大于/小于阈值,pwm6/7有一半时间正常锁存,另外一半不正常的是在半周期内在靠近zero或period时多出来20ns的高电平,20ns高电平不多不少一直是这么长时间。