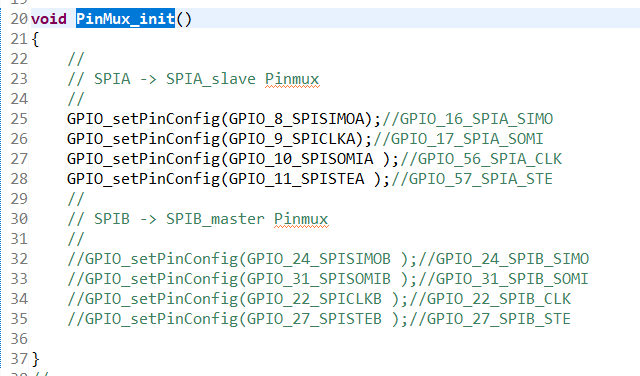

两块开发板 SPI fifo 主从通讯

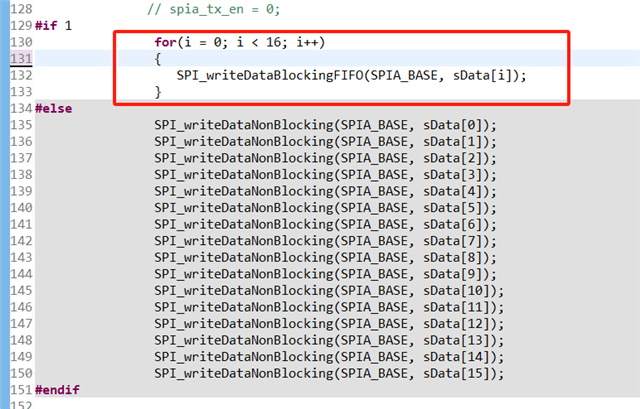

master主机:使用FIFO发送

uint16_t sData[16] = {0x111,0x222,0x333,0x444,0x555,0x666,0x777,0x888,0x999,0xaaa,0xbbb,0xccc,0xddd,0xeee,0xa5a5,0xb6b6}; // Send data buffer

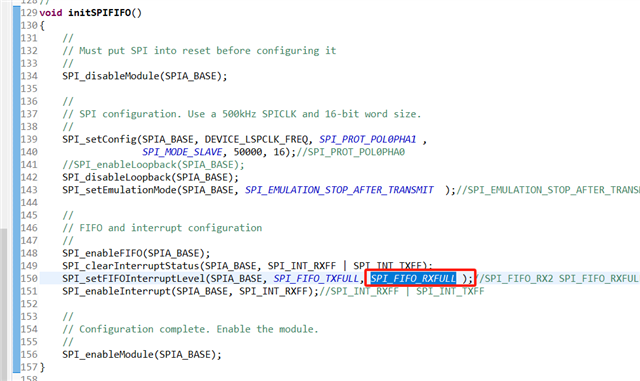

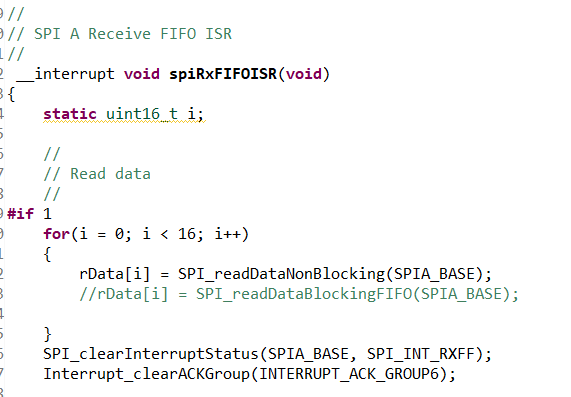

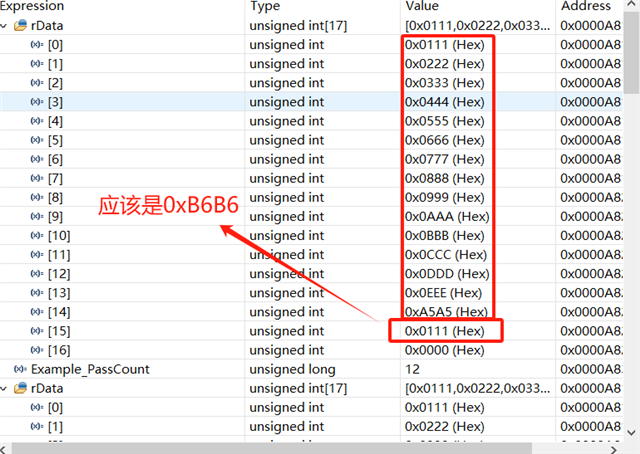

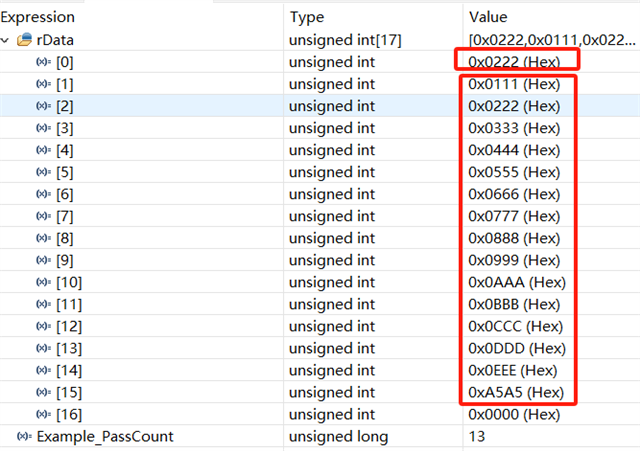

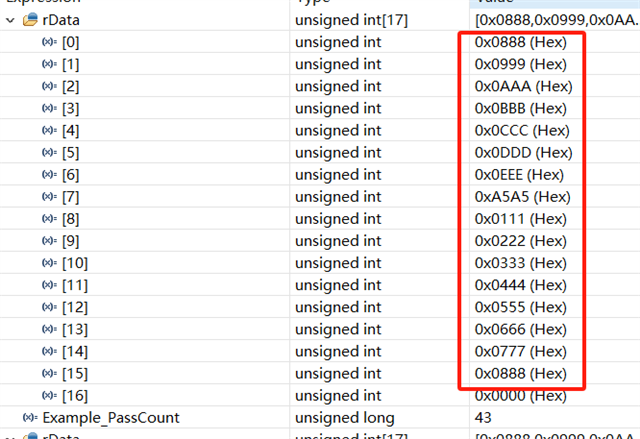

slave从机:FIFO接收

中断接收

问题点 1:接收到的数据缺少最后一个 0xB6B6

问题2:接收数据错位 ,正确的应该是应该是 0x0111-0xEEE 0xA5A5 0xB6B6

请问是哪里配置有问题吗?