目前硬件上 X1 X2脚接了外部无源晶振20M,CLKIN接地。使用函数

void InitSysCtrl(void)

{

// Disable the watchdog

DisableDog();

// Initialize the PLL control: PLLCR and CLKINDIV

// DSP28_PLLCR and DSP28_CLKINDIV are defined in DSP280x_Examples.h

InitPll(DSP28_PLLCR,DSP28_CLKINDIV);

// Initialize the peripheral clocks

InitPeripheralClocks();

}

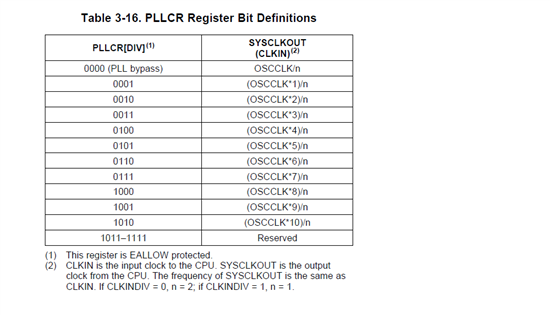

在“DSP280X_Eamples.h”中定义了

#define DSP28_CLKINDIV 0 // Enable /2 for SYSCLKOUT

#define DSP28_PLLCR 10

但是没有得到想要的晶振频率。从例子中也找不到配置使用X1 X2引脚的晶振。求解!!!!!!!!!!!!查看了很多例子InitSysCtrl()函数都一样,不知道是否还有其他文件有关时钟的配置???

可以确认硬件没有虚焊,晶振有起震。

附件为工程,请大神给予帮助