Other Parts Discussed in Thread: C2000WARE

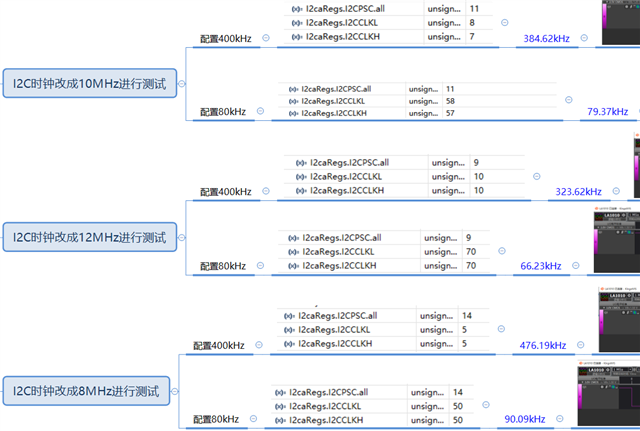

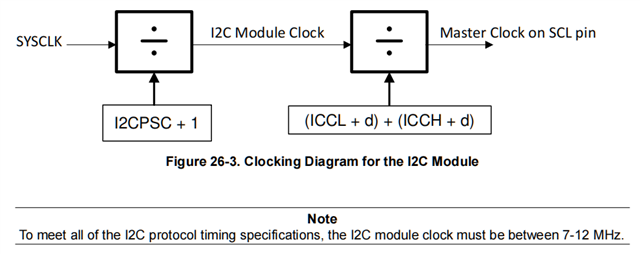

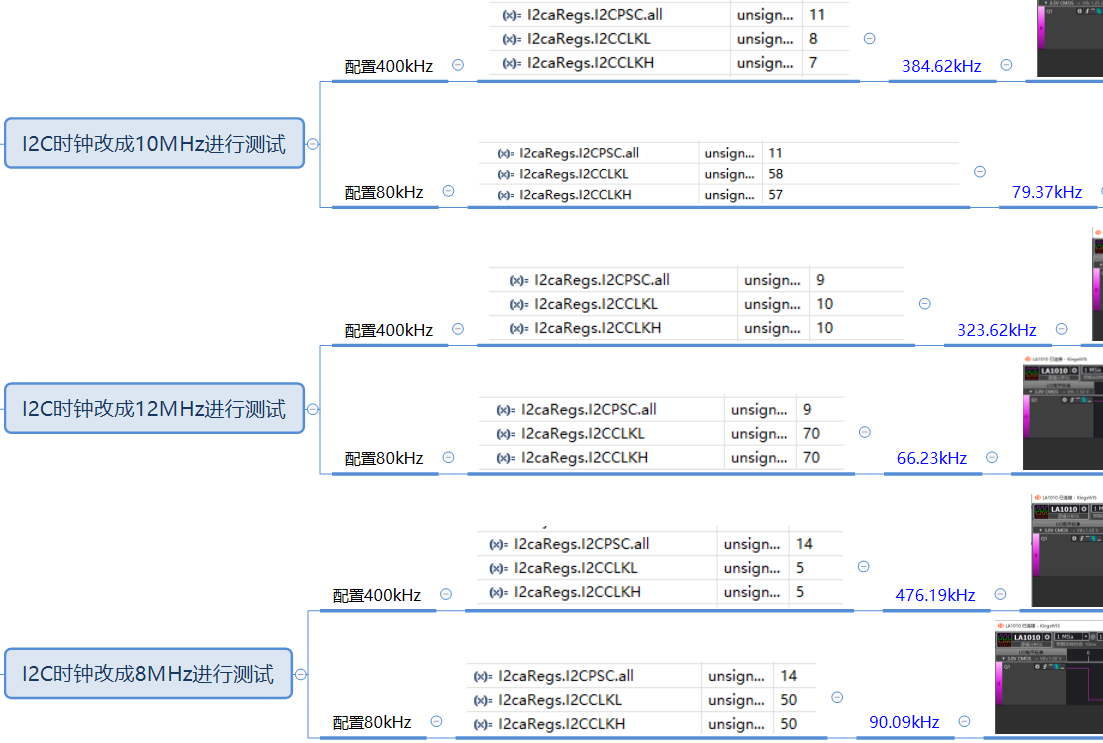

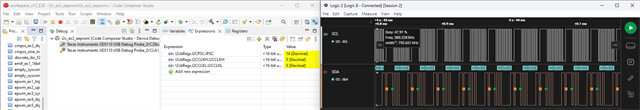

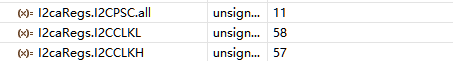

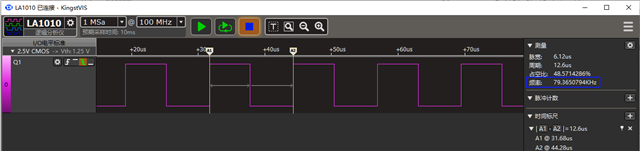

问题现象:I2C时钟频率比预期的小。I2C时钟为10MHz,从测试数据来看从测试数据来看是总时间多了10MHz的一个周期0.1us,核查了参考手册配置无误,测试80kHz时信号频率为1/(2.5us+0.1us)=79.37kHz,400kHz时为1/(12.5us+0.1us)=384.62kHz.。

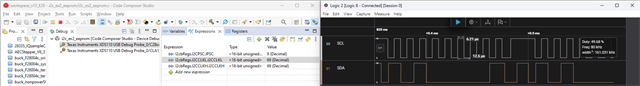

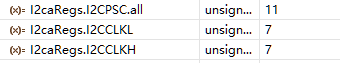

【下图】配置I2C时钟频率为80kHz的参数

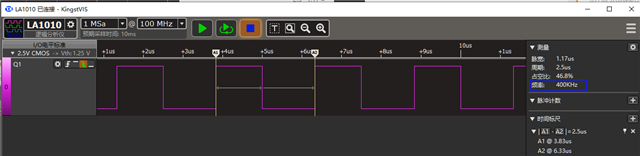

【下图】配置I2C时钟频率为80kHz时实测为79.37kHz

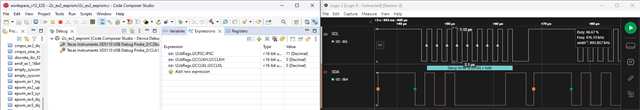

【下图】配置I2C时钟频率为400kHz的参数

【下图】配置I2C时钟频率为400kHz时实测为384.62kHz.

咨询问题:

1、I2C时钟频率比预期的小这种现象是正常的对吧?

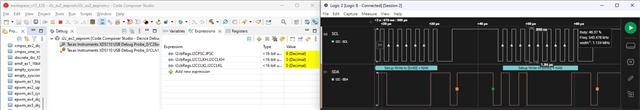

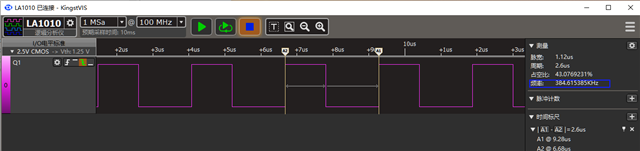

2、可以针对此现象改变参数配置使得I2C时钟频率符合预期,改成实际400kHz时实际对应的是手册里的417kHz的配置,超过了手册所述I2C时钟频率最大400kHz的限制,可以这么使用吗?

【下图】配置实际I2C时钟频率为400kHz的参数

【下图】实测为I2C时钟频率为400kHz