Other Parts Discussed in Thread: RM42L432, HALCOGEN

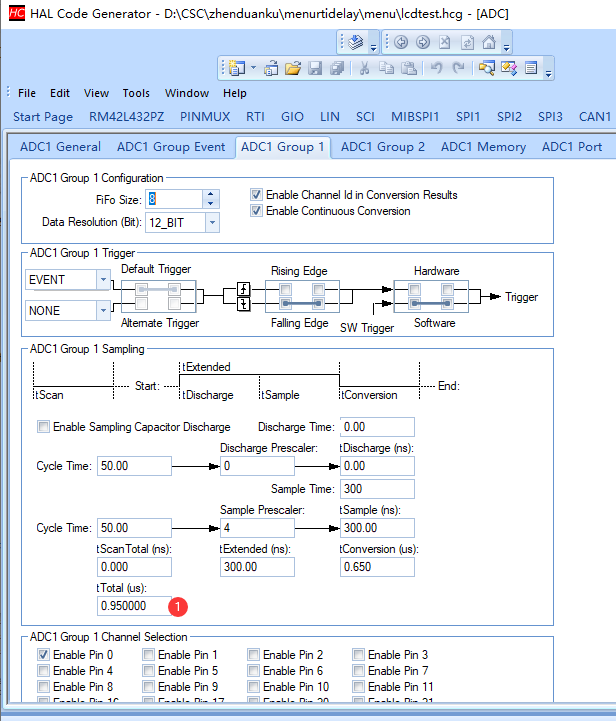

各位好我在使用RM42L432时,配置如下。Totaltime配置为0.95us。按道理来说这时的采样率应该超过1M。但是实际测试只有500k。这个是怎么回事? 谢谢

谢谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.