TI

你好

我看文档上有这样的说明

对于时钟监控部分,首先有外部时钟输出分频器 ECLK,可以从外部监视 CPU时钟频率,引脚可以根据需要配置为 GIO 或 ECLK 引脚。

第二 晶振监视器可以检测到晶振频率是否超过了设定的最大或最小值。当检测到晶振失效时可以选择让芯片复位或将时钟切换到内部低功耗振荡器 LPO上。

此外,PLL 失效监测模块可以监测 PLL 是否出现锁相失败,同样可以选择当检测到 PLL 失效时让 MCU 复位还是切换到内部低功耗振荡器 LPO 或者切换到

外部晶振继续运行。

问题:

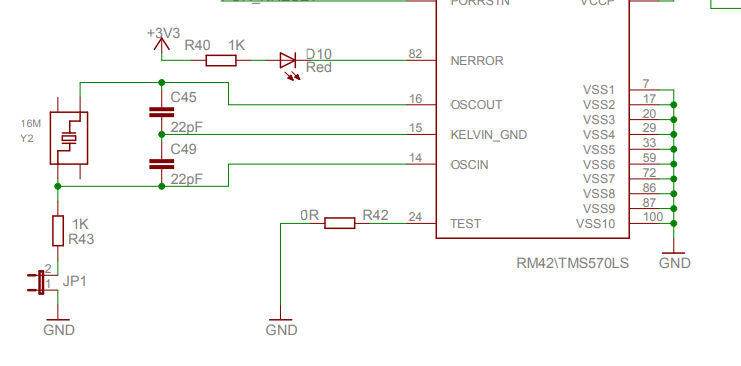

这个外部晶振连接CPU的时候硬件需要特别的设置吗?

如何HCG上设置偏差?需要使能这个功能吗?还是CPU硬件自带的复位.