关于系统时钟这块,我有个问题比较迷惑,就是系统的DCO和FLL。

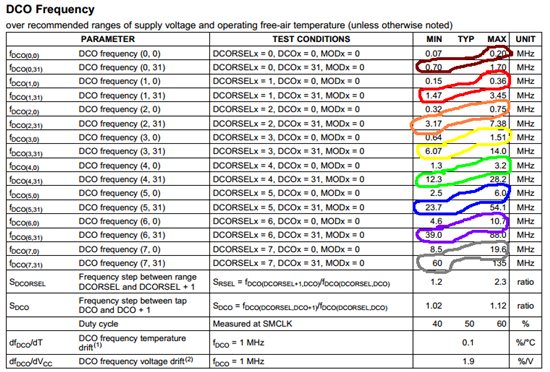

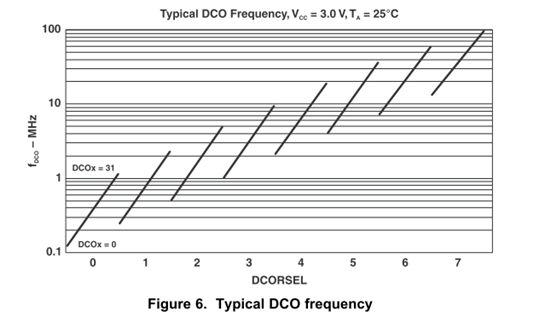

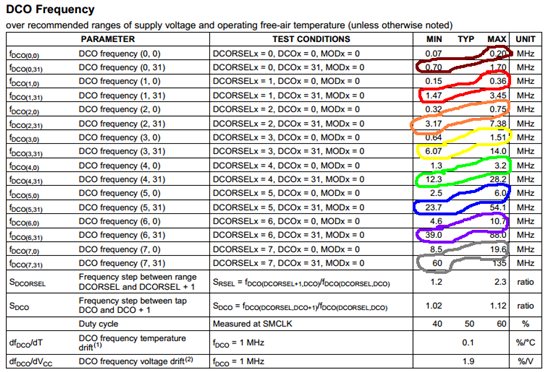

通过阅读MSP430F5529的PDF文档,里面的第59页,给出了不同的DCORSEL位的值对应的DCO频率范围。

但是我有一个地方不明白,就是在官方给出的很多示例文档中,对DCO设置的时候,DCORSEL位的配置和手册里对应的DCO频率范围不相符,不知道为什么?比如按照文档中的说明DCORSEL = 0的时候 DCO频率范围是0.07M到1.7M,但是TI给出的一个例子里是这样的:

if (fsystem <= 630) // fsystem < 0.63MHz

UCSCTL1 = DCORSEL_0;

else if (fsystem < 1250) // 0.63MHz < fsystem < 1.25MHz

UCSCTL1 = DCORSEL_1;

else if (fsystem < 2500) // 1.25MHz < fsystem < 2.5MHz

UCSCTL1 = DCORSEL_2;

else if (fsystem < 5000) // 2.5MHz < fsystem < 5MHz

UCSCTL1 = DCORSEL_3;

else if (fsystem < 10000) // 5MHz < fsystem < 10MHz

UCSCTL1 = DCORSEL_4;

else if (fsystem < 20000) // 10MHz < fsystem < 20MHz

UCSCTL1 = DCORSEL_5;

else if (fsystem < 40000) // 20MHz < fsystem < 40MHz

UCSCTL1 = DCORSEL_6;

else

UCSCTL1 = DCORSEL_7;

按照TI的注释,要得到0.63M到1.25M的频率,需要设置DCORSEL的值为1,但是手册里给出的是0.63M到1.25M的频率完全在DCORSEL=0(0.07M到1.7M)的范围内,为什么要设置DCORSEL为1呢,为0就可以了啊,还有这个例子的后面几句,结合注释,它设置的频率范围和手册里的都对应不上啊,这是怎么回事呢?很困惑...