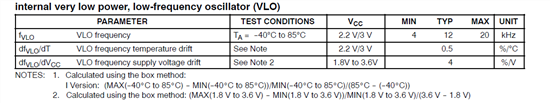

辅助时钟ACLK使用VLO晶振;

UART配置为ACLK的主时钟;

但是用串口助手调试,发现并不会进入UART接收中断。

难道ACLK没有工作,还是配置错误?

另外,我使用SMCLK作为UART主时钟时,正常工作。

附上串口初始化配置程序和基本时钟系统配置程序:

void UART_initial(void)//UART模块配置

{

P1SEL = BIT1 + BIT2;//P1.1&P1.2 SECOND FUNCTION

P1SEL2 = BIT1 + BIT2;

P1DIR = BIT2 + BIT4;//P1.2 P1.4 OUTPUT ,P1.1 RX

UCA0CTL1 |= UCSWRST;// UART RESET

UCA0CTL1 |= UCSSEL_1;// ACLK 12kHz VL Oscillator

UCA0BR0 = 1;//104

UCA0BR1 = 0;

UCA0MCTL = UCBRS0+UCBRS1;//generate 9600BPS

UCA0CTL1 &= ~UCSWRST;// OPERATION

IE2 |= UCA0RXIE;//OPEN RX interrupt

}

void Clk_initial(void)

{

if(CALBC1_1MHZ==0xFF || CALDCO_1MHZ==0xFF)

{

while(1);

}

DCOCTL = 0; // Select lowest DCOx and MODx settings

BCSCTL1 = CALBC1_1MHZ; // Set RSEL2=0X04:RSEL4 + XT20FF=0X80

DCOCTL = CALDCO_1MHZ; //Set DCO1=0x40:DCO2

BCSCTL2 = SELM0; //SELM0=0x40 1MHz DCO FOR MCLK&SMCLK internal Resistor

BCSCTL3|=LFXT1S_2;//guidesheet上面没写BCSCTL3,这里选择ACLK的时钟源为内部VLO

}

烦劳各位了!