如上图.请教Susan,看有没有办法。解决?

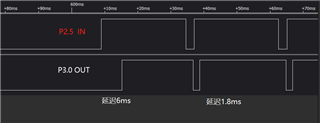

1)p2.5长时间低电平,突然收到上升沿中断在激活到PWM输出,延迟比较久,对比后面第1次6ms多,后面的1.8-1.9ms

2)p2.5高电平占空比不能调的非常大,如果超过90%之后,可能导致上升沿中断不触发了?导致pwm输出功能失效。

3)p2.5高电平占空比,会影响中断启动延迟,如1)。调小占空比,会导致PWM输出延迟变长。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

p2.5长时间低电平

请问您P2.5处的触发以及中断服务程序是怎样的?若是可以的话,请给一下代码,谢谢

问题其实可以收敛到,只是IO中断响应延迟的问题。

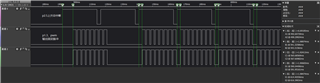

简单实验如下:P2.5变化中断,同步改变P3.0状态。第一次触发响应延迟6ms,后续快速周期性触发1.8ms左右

#include <msp430.h>

void Cpu_int(void)

{

if (CALBC1_1MHZ==0xFF)

{

while(1);

}

DCOCTL = 0;

BCSCTL1 = CALBC1_1MHZ;

DCOCTL = CALDCO_1MHZ;

}

void main(void)

{

WDTCTL = WDTPW + WDTHOLD; // Stop WDT

Cpu_int();

//P2.5 上升沿输入中断设置

P2DIR|=BIT5;

P2REN&=~BIT5;

P2IES&=~BIT5;

P2OUT&=~BIT5;

P2IFG&=~BIT5;

P2DIR&=~BIT5;

P2IE|=BIT5;

//p3.0 trigger out

P3DIR |= BIT0;

//P3REN|=BIT0;

_EINT();

__low_power_mode_1();

}

//mcu-triggerin

#pragma vector=PORT2_VECTOR

__interrupt void Port_2(void)

{

P2IFG&=~(BIT5 | BIT4);

if(P2IN&BIT5) //p2.5: mcu-triggerIn

{

P3OUT|=BIT0;

P2IES|=BIT5;

}else{

P3OUT&=~BIT0;

P2IES&=~BIT5;

}

}