你好我想知道运行一行代码对应的时钟是哪一个时钟因为这里要设置在串口接收到与后回复之间有一段时间,这段时间只可能是代码运行的时间,我想尽可能缩短这段时间的话可能要知道对应一行代码所需要的时间。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你好我想知道运行一行代码对应的时钟是哪一个时钟因为这里要设置在串口接收到与后回复之间有一段时间,这段时间只可能是代码运行的时间,我想尽可能缩短这段时间的话可能要知道对应一行代码所需要的时间。

,这段时间只可能是代码运行的时间,我想尽可能缩短这段时间的话可能要知道对应一行代码所需要的时间。

您可以在CCS内使用时钟功能来查看代码运行的时钟周期

即使用CCS自带的Clock Cycle功能(run->clock->enable, clock 清零,需要CCS5以上版本)

我想知道运行一行代码对应的时钟是哪一个时钟

这取决于您的时钟配置,您是如何配置的呢?

我配置的是ACLK是32.725khz,MCLK是16MHZ,SMCLK是16MHZ,用的是内部时钟REFOCLK32.725KHZ,DCO是16MHZ。

那您可以之前提到的方式来查看代码运行的时钟周期个数,而后乘以 每个时钟周期代表的时间即可

每个时钟周期代表的时间=1/(时钟频率)

时钟的话,是要看您CSCTL的配置

__bis_SR_register(SCG0); // disable FLL

CSCTL3 |= SELREF__REFOCLK; // Set REFO as FLL reference source

CSCTL0 = 0; // clear DCO and MOD registers

CSCTL1 &= ~(DCORSEL_7); // Clear DCO frequency select bits first

CSCTL1 |= DCORSEL_5; // Set DCO = 16MHz

CSCTL2 = FLLD_0 + 487; // set to fDCOCLKDIV = (FLLN + 1)*(fFLLREFCLK/n)

// = (487 + 1)*(32.768 kHz/1)

// = 16 MHz

__delay_cycles(3);

__bic_SR_register(SCG0); // enable FLL

while(CSCTL7 & (FLLUNLOCK0 | FLLUNLOCK1)); // FLL locked

CSCTL4 = SELMS__DCOCLKDIV | SELA__REFOCLK;

这是我的一个时钟定义,大概是一个内频16MHZ,因为现在UART0被占用没法一边debug,一边调试。我有不太明白哪一个时钟比如,ACLK,还是MCLK或着SMCLK或着DCO是对应的代码运行的时钟频率。

CSCTL4 = SELMS__DCOCLKDIV | SELA__REFOCLK;

即

#define SELMS__DCOCLKDIV (0x0000) /* MCLK and SMCLK Source Select DCOCLKDIV */

#define SELA__REFOCLK (0x0100) /* ACLK Source Select REFOCLK */

我有不太明白哪一个时钟比如,ACLK,还是MCLK或着SMCLK或着DCO是对应的代码运行的时钟频率。

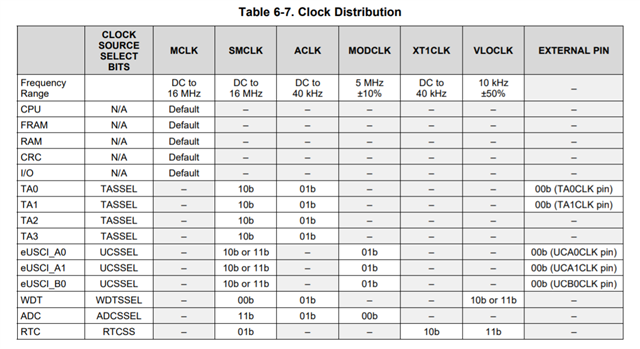

请参考下表