今天做了个实验,用于测试改变MSP430x2xxACLK分频系数后,新的ACLK达到稳定时间。因为在datasheet和user guide上,没有找到相关ACLK改变分频系数后相关描述和说明,故使用MSP430G2553对此作了一个简单的测试。分享一下。O(∩_∩)O~

结论:改变ACLK的分频系数后,ACLK首先会按照之前的配置(分频系数)完成当前ACLK周期输出,且每个完整的ACLK周期输出是以低电平结束的,然后才会按照新的分频系数输出新的ACLK。

建议:建议客户在更改ACLK分频系数后,至少延时一个之前ACLK周期的时间,以等待新的ACLK分频系数生效。

详细测试步骤:

设置MSP430G2553 MCLK=SMCLK=1MHz, ACLK=LFXT1=32768Hz

1. 首先设置 DIVAx= /1,ACLK=LFXT1=32768Hz。然后延时0.3ms, 约为 10*ACLK cycles;

2.设置 DIVAx= /8, 则 ACLK=32768/8=4096Hz;

3. 延时 0.7ms, 约为3*ACLK cycles,然后设置DIVAx= /1 ,ACLK=LFXT1=32768Hz。

另外可以更改延时时间,让ACLK分频改变发生在ACLK的不同时间 (高电平或低电平)来验证结论。

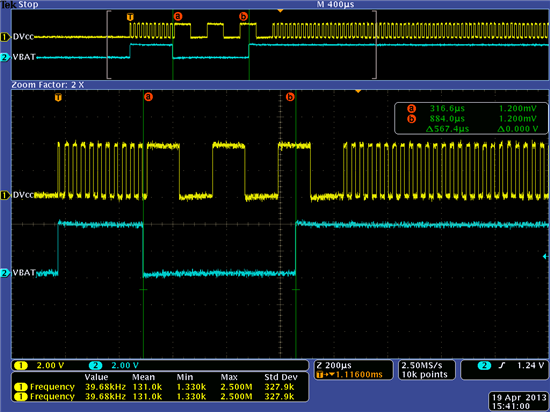

测试图片:

(Channel1: ACLK; Channel 2: P1.2)

A: ACLK DIVx 1st change: ACLK high level; 2nd change, ACLK low level

B:ACLK DIVx 1st change: ACLK low level; 2nd change, ACLK high level

见附件。