__bis_SR_register(SCG0); // Disable the FLL control loop

UCSCTL0 = 0x0000; // Set lowest possible DCOx, MODx

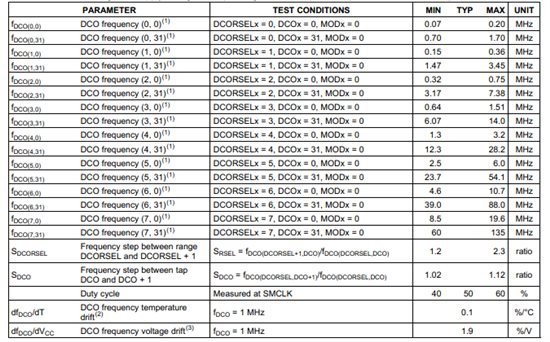

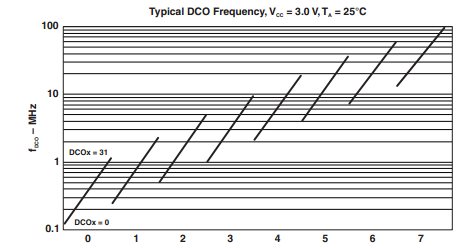

UCSCTL1 = DCORSEL_5; // Select DCO range 16MHz operation

UCSCTL2 = FLLD_1 + 249; // Set DCO Multiplier for 8MHz

// (N + 1) * FLLRef = Fdco // (249 + 1) * 32768 = 8MHz // Set FLL Div = fDCOCLK/2

__bic_SR_register(SCG0); // Enable the FLL control loop

请问一下这里的UCSCTL1 = DCORSEL_5; 怎么得到DCO最大为16MHz,求解。谢谢!