目的:将ACLK、MCLK配置为XT132.768KHZ。

但是:实际测量MCLK为876KHZ左右,ACLK虽然是32.768KHZ,但我感觉还是内部的REFO。

请问是不是我的设置有什么问题啊

#include <msp430.h>

void main(void)

{

P1SEL |= BIT0;

P1DIR |= BIT0;//测量ACLK用

P2SEL |= BIT2;

P2DIR |= BIT2;//测量SMCLK用

P7SEL |= BIT7;

P7DIR |= BIT7;//测量MCLK用

P5SEL |= BIT4|BIT5; //将IO配置为XT1功能,电路板上晶振接于这两脚

UCSCTL6 |= XCAP_3; //配置电容为12pF

UCSCTL6 &= ~XT1OFF; //使能XT1

while(SFRIFG1 & OFIFG) //如果有时钟错误

{

UCSCTL7 &=~(XT2OFFG+DCOFFG+XT1LFOFFG);//清除3种时钟错误标志

SFRIFG1&=~(OFIFG);//清除时钟错误标志位

}

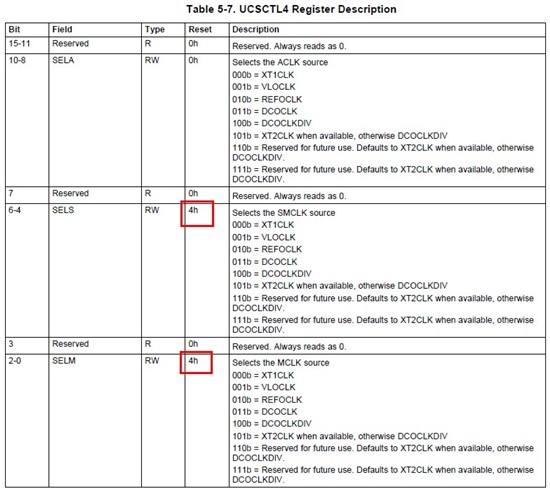

UCSCTL4&=(UCSCTL4&(~(SELA_7|SELM_7)))|SELS_0|SELM__XT1CLK|SELA_0;//将ACLK和MCLK时钟源配置为XT1

}