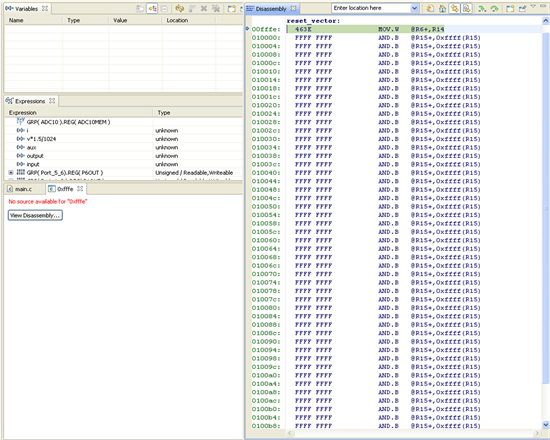

如图,这个错误出现在进入ADC12中断的时候,我把ADC12这部分代码一并附上,这是什么原因啊?该怎么解决?

void ADC12_Initial(void){

P6SEL &= ~BIT6;

ADC12CTL0 &= ~ADC12ENC; // Set to 0

// Conversion memory start address, Timer Trigger, Repeat Single-Channel Conversion, Pulse-Mode, *ADC12 Clock source select SMCLK*

ADC12CTL1 = ADC12CSTARTADD_0 + ADC12SHS_1 + ADC12CONSEQ_2 + ADC12SHP /*+ ADC12SSEL_3*/;

// ADC On, 8 ADC12CLK Cycles, ADC Voltage Reference On, Voltage Reference 2.5V

ADC12CTL0 = ADC12ON + ADC12SHT0_1 + ADC12REFON + ADC12REF2_5V;

// ADC12 resolution 12 bits

ADC12CTL2 = ADC12RES_2;

// ADC Input select, V(R+) = VREF+ and V(R-) = AVSS

ADC12MCTL0 |= ADC12INCH_6 + ADC12SREF_1;

while (REFCTL0 & REFGENBUSY) // If Ref generator busy, wait

REFCTL0 |= REFVSEL_2 + REFON; // Select internal Ref = 2.5V, Internal Reference On

ADC12CTL0 |= ADC12ENC;

P6DIR &= ~BIT6; // Set P6.6 A6

TA0CTL = TASSEL_2 + MC_1; // Choose SMCLK, Up-Mode

TA0CCR1 = 49; // 5MHz/100KHz - 1 = 49

TA0CCTL1 = CAP + CCIE + CCIFG + OUTMOD_3; // Set/reset

TA0CTL |= TACLR + TAIE; // Enable interrupt, Clear TAR

__bis_SR_register(LPM0_bits + GIE); // Enter LPM0 w/ interrupts.在这里出错

}

#pragma vector=ADC12_VECTOR

__interrupt void ADC12ISR (void)

{

switch(__even_in_range(ADC12IV,34))

{

case 0: break; // Vector 0: No interrupt

case 2: break; // Vector 2: ADC overflow

case 4: break; // Vector 4: ADC timing overflow

case 6:

{

ADC12CTL0 |= ADC12SC;

ADC_Results[index] = ADC12MEM0;

}

break; // Vector 6: ADC12IFG0

case 8: break; // Vector 8: ADC12IFG1

case 10: break; // Vector 10: ADC12IFG2

case 12: break; // Vector 12: ADC12IFG3

case 14: break; // Vector 14: ADC12IFG4

case 16: break; // Vector 16: ADC12IFG5

case 18: break; // Vector 18: ADC12IFG6

case 20: break; // Vector 20: ADC12IFG7

case 22: break; // Vector 22: ADC12IFG8

case 24: break; // Vector 24: ADC12IFG9

case 26: break; // Vector 26: ADC12IFG10

case 28: break; // Vector 28: ADC12IFG11

case 30: break; // Vector 30: ADC12IFG12

case 32: break; // Vector 32: ADC12IFG13

case 34: break; // Vector 34: ADC12IFG14

default: break;

}

}