各位同事朋友,我有个关于MSP430F673X问题请教大家帮忙!

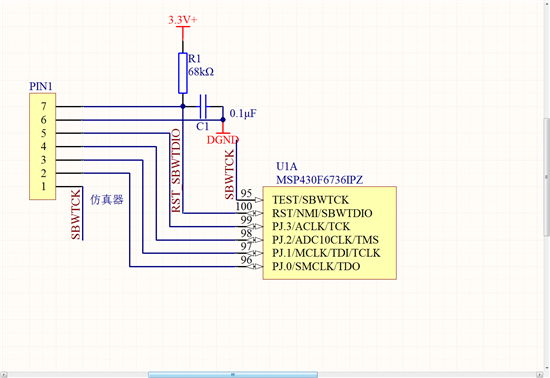

1、使用TI并口的JATG 仿真器无法找到硬件,如果使用TI的3线SW可以下载,这个为什么?

PIN的2脚接JATG的1脚,3脚接JATG的3脚,4脚接JATG的5脚,5脚接JATG的7脚,6脚接JATG的9脚,7脚接JATG的11脚。

我用F427是可以用并口下载得。

2、如何设置RTCPS0CTL,并且我想知道这个是做什么用得。

3、RTC我看计数模式,和日历模式,是不是二选一。

4、在LPM3模式下是否在走?

5、以下代码CPU 是否工作在16M时钟下?SMCLK是不是4M

UCSCTL6 &= ~XT1OFF; //打开

UCSCTL6 |= SMCLKOFF|XCAP_3;

do

{

UCSCTL7 &= ~(XT2OFFG | XT1LFOFFG | DCOFFG);

SFRIFG1 &= ~OFIFG; // Clear fault flags

__delay_cycles(2000);

} while (SFRIFG1 & OFIFG); // Test oscillator fault flag

__delay_cycles(48000);

__bis_SR_register(SCG0); // Disable the FLL control loop

UCSCTL0= 0; // Set lowest possible DCOx=31, MODx=0

UCSCTL1 = DCORSEL_7; // Select DCO range 24MHz operation

UCSCTL2 |=FLLD_1|(243*2); //16M

__bic_SR_register(SCG0); // Enable the FLL control loop

请各位朋友帮忙解答一下?