1、芯片:MSP430F5438A

2、外接晶振:25MHz

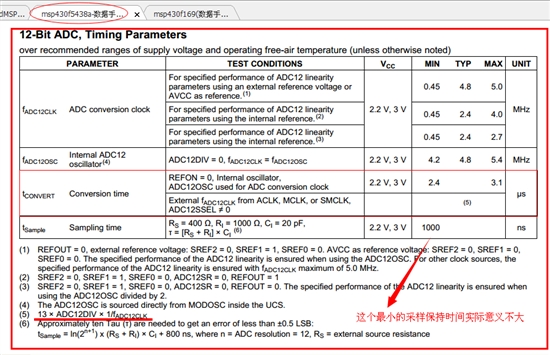

3、ADC时钟选择MCLK=25MHz的5分频,即ADC12CLK=5MHz,即0.2us

4、采样保持时间为:16个ADC12CLK cycles,即Tsample=4*0.2*16=12.8us???我这样算对吗??

5、转换时间公式:13 × ADC12DIV × 1/fADC12CLK,即13*5*0.2us=13us

那么我的ad采样一个点转换完的时间是:采样保持时间+转换时间=12.8+13us=25.8us,按照这么算我的采样率才:1/25.8=38.75Ksps???

请问我的上述计算方法对吗?

附件1:我的adc初始化代码

void ADC12_Init(void)

{

P6SEL |=BIT0 + BIT1 + BIT2; // Enable VeREF+ & A/D channel A0

ADC12CTL0 = ADC12ON+ADC12MSC+ADC12SHT0_2; // Turn on ADC12_A, extend sampling time

// to avoid overflow of results

ADC12CTL1 = ADC12SSEL_2 //时钟选择为:MCLK

+ADC12DIV_4 //时钟分频为:4

+ADC12SHP //采样信号源自采样定时器

+ADC12CONSEQ_3; //序列通道多次采样

ADC12MCTL0 = ADC12INCH_0; // ref+=AVcc, channel = A0

ADC12MCTL1 = ADC12INCH_1; // ref+=AVcc, channel = A1

ADC12MCTL2 = ADC12INCH_2+ADC12EOS; // ref+=AVcc, channel = A2, end seq.

}

附件2:我的时钟等代码如下

int main(void)

{

WDTCTL = WDTPW + WDTHOLD; // Stop WDT

//##############################################################################

//Increase Vcore setting to level3 to support fsystem=25MHz

SetVCore(PMMCOREV_1);//Set Vcore level 3 to match higher SVS levels

SetVCore(PMMCOREV_2);//Set Vcore level 3 to match higher SVS levels

SetVCore(PMMCOREV_3);//Set Vcore level 3 to match higher SVS levels

Feed_Dog;//喂外部狗CAT1023,2013-05-06

ExCLK_Init();

//XT2_Start(XT2DRIVE_3);//设置XT2DRIVE_3可以提高对晶振的驱动能力,2013-04-04

Feed_Dog;//喂外部狗CAT1023,2013-05-06

DISABLE_SVSL(); // SVS Low side is turned off

DISABLE_SVML(); // Monitor low side is turned off

DISABLE_SVMH(); // Monitor high side is turned off

ENABLE_SVSH(); // SVS High side is turned on

ENABLE_SVSH_RESET();

SVSH_ENABLED_IN_LPM_FULL_PERF(); // Full performance mode,stays on in LPM3

// Wait until high side, low side settled

while(((PMMIFG & SVSMLDLYIFG) == 0)&&((PMMIFG & SVSMHDLYIFG) == 0));

// SVSH turns off in LPM3,power-save

CLEAR_PMM_IFGS();

// SVS protection set at Level 3/5

PMMCTL0_H = 0xA5;

SVSMHCTL |= SVSHRVL_3 + SVSMHRRL_5;

while((PMMIFG & SVSMHDLYIFG) == 0); // Level reached?

PMMCTL0_H = 0x00;

CLEAR_PMM_IFGS();

//##############################################################################

while(1)

{

;

}

}

#pragma vector=UNMI_VECTOR

__interrupt void NMI_ISR(void)

{

uint16_t status=0;

do

{

// If it still can't clear the oscillator fault flags after the timeout, trap and wait here.

status = Clear_All_Osc_Flags(1000);

} while(status != 0);

}

//******************************************************************************

//描述:外部高速时钟初始化,使用xM晶振

//输入:无 输出:无

//******************************************************************************

static void ExCLK_Init(void)

{

P5SEL |= 0x0C; // Port select XT2

//P7SEL |= 0x03; // Port select XT1

UCSCTL6 &= ~XT2OFF; // Enable XT2

//下面用SELREF__XT2CLK也可以,2013-03-29

UCSCTL3 |= SELREF_2;// FLLref = REFO

// Since LFXT1 is not used,

// sourcing FLL with LFXT1 can cause

// XT1OFFG flag to set

UCSCTL4 |= SELA_2; // ACLK=REFO,SMCLK=DCO,MCLK=DCO

UCSCTL6 |= XT2DRIVE_3;// Decrease XT2 Drive according to expected frequency

//+ XT2BYPASS;//XT2 sourced from external pin

// Loop until XT1,XT2 & DCO stabilizes

do

{

UCSCTL7 &= ~(XT2OFFG + XT1LFOFFG + XT1HFOFFG + DCOFFG);

// Clear XT2,XT1,DCO fault flags

SFRIFG1 &= ~OFIFG; // Clear fault flags

}while(SFRIFG1&OFIFG);// Test oscillator fault flag

UCSCTL4 |= SELA__XT2CLK + SELS__XT2CLK + SELM__XT2CLK;//时钟选择

//UCSCTL5 |= DIVA_1;//ACLK=XT2CLK/2,SMCLK=XT2CLK,MCLK=XT2CLK,2013-04-03

}