IO可以工作了,但是想问下为什么需要进行 PM5CTL0 &= ~LOCKLPM5; 设置。

还有,其他引脚在用IO功能时也需要做类似的操作吗 ?

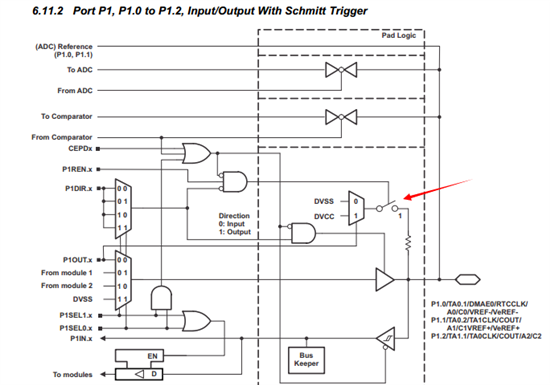

我这样设置P4.6却得不到期望的输出,怎么解决

P1OUT &= ~0x01; // Clear P1.0 output latch for a defined power-on state

P1DIR |= 0x01; // Set P1.0 to output direction

P1REN |=0x01;

P1SEL1=0;

P1SEL0=0;

P4OUT &= ~0x06; // Clear P4.6 output latch for a defined power-on state

P4DIR |= 0x06; // Set P4.6 to output direction

P4REN |=0x06;

P4SEL1=0;

P4SEL0=0;

// to activate previously configured port settings

while(1)

{

P1OUT ^= BIT0; // Toggle LED

P4OUT ^= BIT6; // Toggle LED

__delay_cycles(1000000);

}

另外能不能再分别给个该单片机的SPI和Uart通信例程。