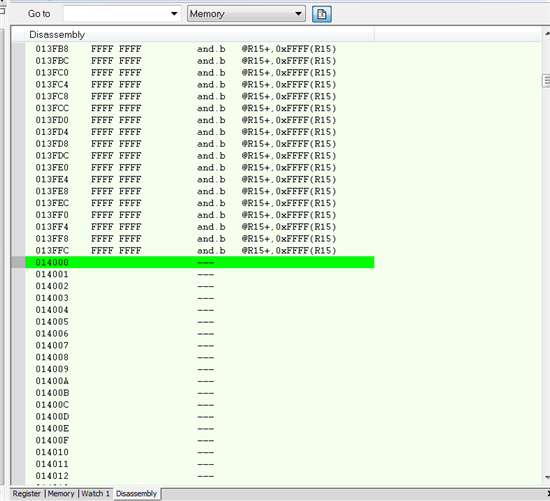

如图,

郁闷,为何会执行到这个地方,换了个片子也是。

用的672x

void main( void )

{

// Stop watchdog timer to prevent time out reset

WDTCTL = WDTPW + WDTHOLD;

__disable_interrupt();

ClkInit();

P4SEL &= ~BIT1; P4DIR |= BIT1; //蜂鸣器控制脚

Timer2_A2_Init();

__enable_interrupt();

while(1)

{

if( Button_Scan(1) == 1 )

{

P4OUT |= BIT1;

_delay_ms(50);

}

else

{

P4OUT &= ~BIT1;

}

}

}

void main( void )

{

// Stop watchdog timer to prevent time out reset

WDTCTL = WDTPW + WDTHOLD;

__disable_interrupt();

ClkInit();

P4SEL &= ~BIT1; P4DIR |= BIT1; //蜂鸣器控制脚

Timer2_A2_Init();

__enable_interrupt();

while(1)

{

if( Button_Scan(1) == 1 )

{

P4OUT |= BIT1;

_delay_ms(50);

}

else

{

P4OUT &= ~BIT1;

}

}

}