Part Number: MSPM0G3519

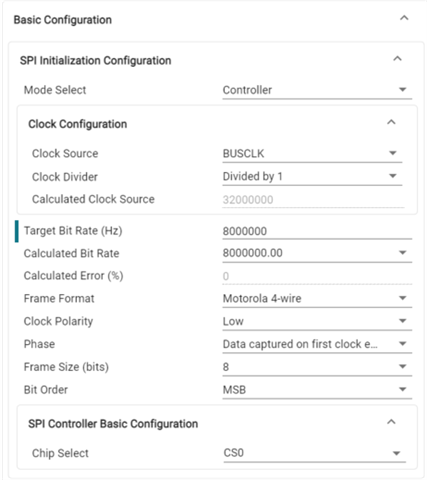

When configuring the SPI interface on the MSPM0G3519 as a master, how should I calculate the safe operating frequency if the connected slave device specifies a minimum clock period of 10 ns? Should I set the SPI baud rate divider strictly to stay under that limit, or does the internal clock stretching or delay in the MSPM0G3519 affect that timing in practice?