单片机 TM4C123GXL,芯片GH6PM

CCS 版本6.0.1

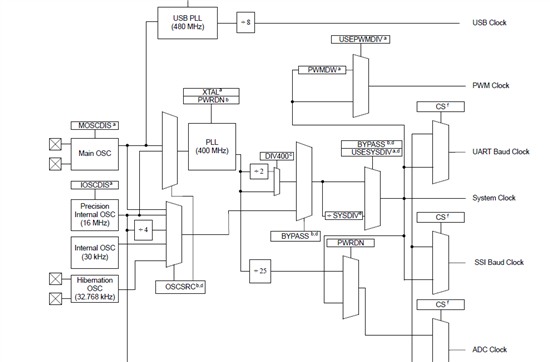

之前程序时钟设置为: SysCtlClockSet(SYSCTL_SYSDIV_64|SYSCTL_USE_OSC|SYSCTL_OSC_MAIN |SYSCTL_XTAL_16MHZ);

在将时钟改为18MHz时,即SysCtlClockSet(SYSCTL_SYSDIV_64|SYSCTL_USE_OSC|SYSCTL_OSC_MAIN |SYSCTL_XTAL_18MHZ);

使用示波器观察对应GPIO口,PWM波频率没有改变,这是为什么呢?

附程序如下:

/*利用PWMO,PWM1产生200HZ和400Hz 50%占空比的方波*/

#include <stdint.h>

#include <stdbool.h>

#include "inc/hw_memmap.h"

#include "inc/hw_types.h"

#include "driverlib/sysctl.h"

#include "driverlib/rom.h"

#include "driverlib/gpio.h"

#include "driverlib/pwm.h"

#include "driverlib/fpu.h"

#include "driverlib/pin_map.h"

int main (void)

{

//使能FPU

FPUEnable();

FPULazyStackingEnable();

//设置系统时钟为16MHz

SysCtlClockSet(SYSCTL_SYSDIV_64|SYSCTL_USE_OSC|SYSCTL_OSC_MAIN |SYSCTL_XTAL_16MHZ);

//使能PWM0模块,使能PWM0和PWM1输出所在GPIO

SysCtlPeripheralEnable(SYSCTL_PERIPH_PWM0);

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOB);

GPIOPinTypePWM(GPIO_PORTB_BASE, GPIO_PIN_4|GPIO_PIN_5|GPIO_PIN_6|GPIO_PIN_7);

GPIOPinConfigure(GPIO_PB6_M0PWM0);

GPIOPinConfigure(GPIO_PB7_M0PWM1);

GPIOPinConfigure(GPIO_PB4_M0PWM2);

GPIOPinConfigure(GPIO_PB5_M0PWM3);

//驱动电流8MA,推挽输出

GPIOPadConfigSet(GPIO_PORTB_BASE,GPIO_PIN_4|GPIO_PIN_5|GPIO_PIN_6|GPIO_PIN_7,

GPIO_STRENGTH_8MA,GPIO_PIN_TYPE_STD);

// PWM时钟配置

SysCtlPWMClockSet(SYSCTL_PWMDIV_1);

// SysCtlPWMClockSet(SYSCTL_PWMDIV_32);

//配置PWM发生器0:加减计数,不同步

PWMGenConfigure(PWM0_BASE,PWM_GEN_0,PWM_GEN_MODE_UP_DOWN| PWM_GEN_MODE_NO_SYNC);

PWMGenConfigure(PWM0_BASE,PWM_GEN_1,PWM_GEN_MODE_UP_DOWN| PWM_GEN_MODE_NO_SYNC);

//设置PWM发生器0的频率,时钟频率/PWM分频数/n,16M/64/1250=200HZ

PWMGenPeriodSet(PWM0_BASE, PWM_GEN_0, 1250);

//设置PWM发生器1的频率,时钟频率/PWM分频数/n,16M/16/625=400HZ

PWMGenPeriodSet(PWM0_BASE, PWM_GEN_1, 625);

//设置PWM0/PWM1输出的脉冲宽度

PWMPulseWidthSet(PWM0_BASE, PWM_OUT_0,1250/2);

PWMPulseWidthSet(PWM0_BASE, PWM_OUT_1,1250/2);

PWMPulseWidthSet(PWM0_BASE, PWM_OUT_2,625/2);

PWMPulseWidthSet(PWM0_BASE, PWM_OUT_3,625/2);

//使能PWM0和PWM1的输出

PWMOutputState(PWM0_BASE, (PWM_OUT_0_BIT |PWM_OUT_1_BIT| PWM_OUT_2_BIT| PWM_OUT_3_BIT), true);

//使能PWM发生器

PWMGenEnable(PWM0_BASE, PWM_GEN_0);

PWMGenEnable(PWM0_BASE, PWM_GEN_1);

while(1)

{

}

}