Part Number: RM48L952

Other Parts Discussed in Thread: TMDSRM48HDK, HALCOGEN

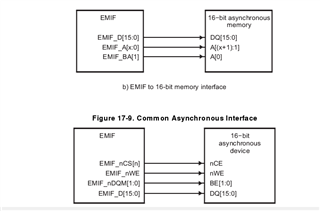

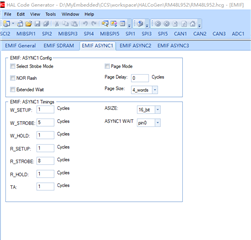

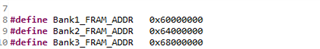

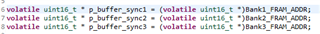

在本应用中使用的是TI开发板TMDSRM48HDK。emif接了一个板载的sdram以及三个异步fram存储器,通过存储窗口观察sdram读写正常,但是异步访问不对,现在将配置和程序贴在下面

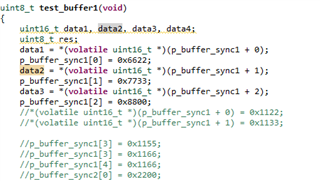

程序代码如下

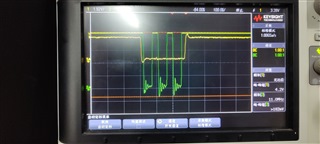

在test_buffer1()中进行读写操作,在存储监测窗口看不到正确变化,用示波器监测写过程的ce 、we脚,发现we脚有异常。在一个写周期内,we脚反复变化,不知道这是什么原因,是不是造成写不进去的根源,希望能得到解答。或者是不是在异步存储配置方面有别的问题。