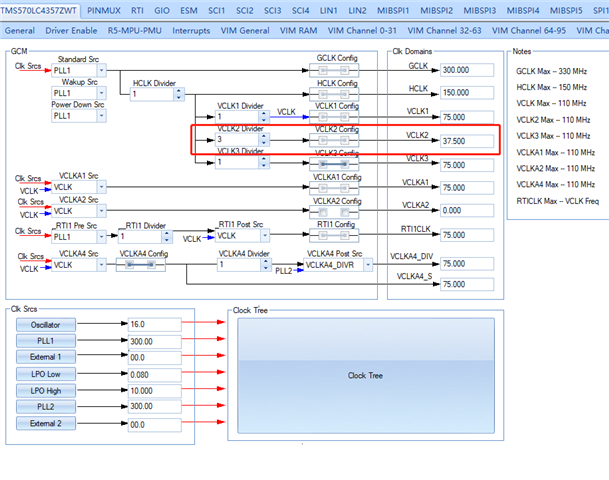

在VCLK2的时钟是75MHZ时,HET1-16产生的PWM频率是正确的。但当VLCK2的时钟为50MHZ和37.5MHZ时,HET1-16产生的PWM频率不正确。

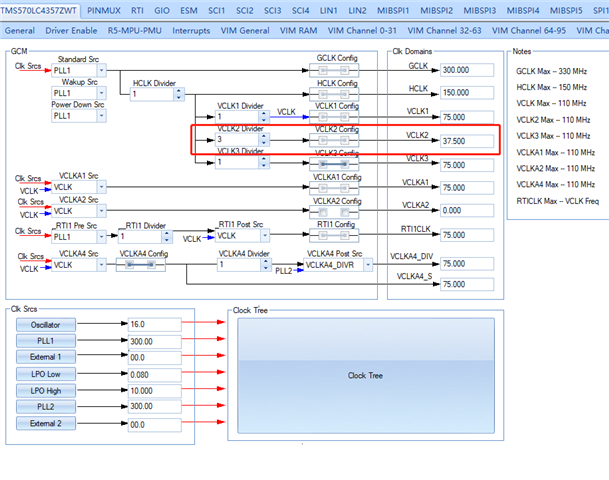

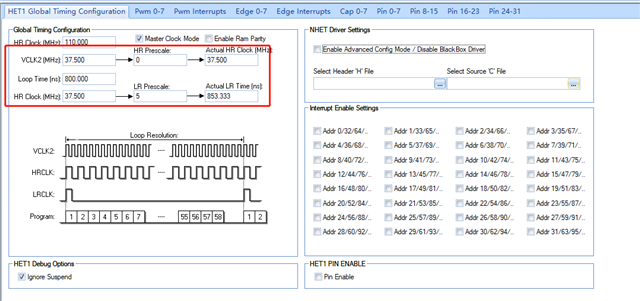

如图:配置VCLK2时钟为37.5MHZ

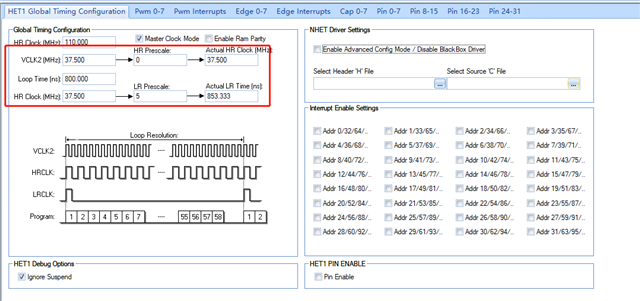

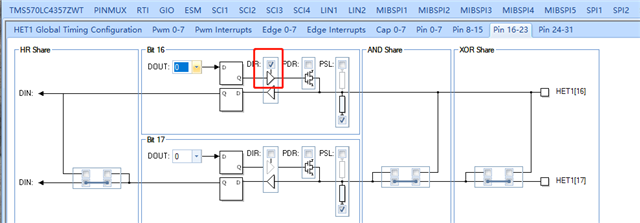

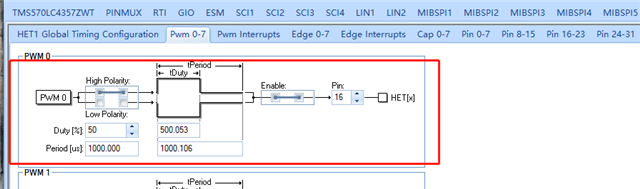

使能N2HET1-16产生频率为1KHZ的频率

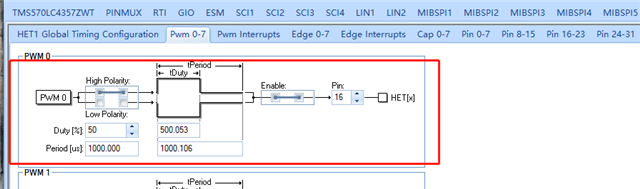

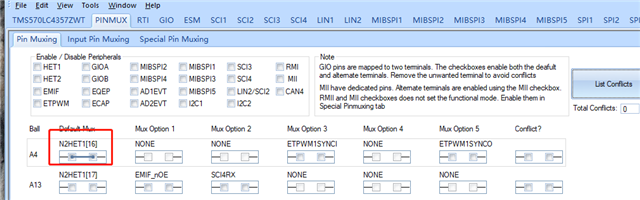

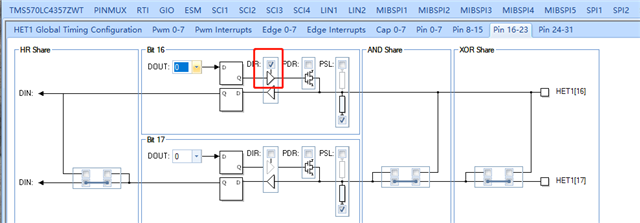

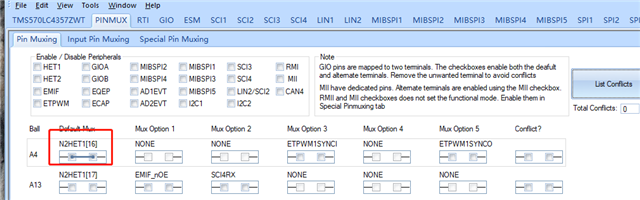

使能N2HET1-16的引脚

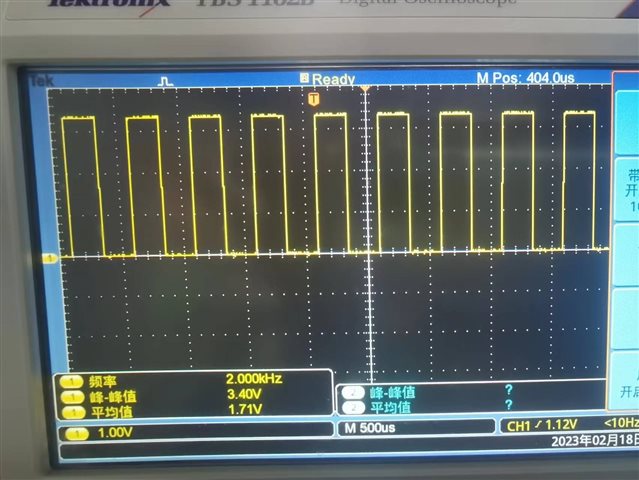

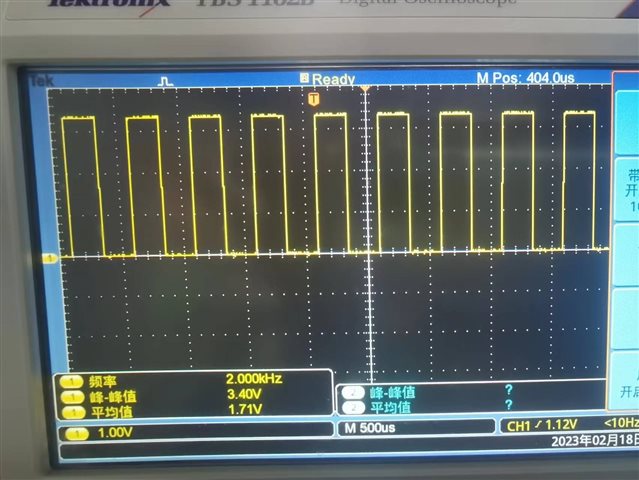

测试到pwm

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

在VCLK2的时钟是75MHZ时,HET1-16产生的PWM频率是正确的。但当VLCK2的时钟为50MHZ和37.5MHZ时,HET1-16产生的PWM频率不正确。

如图:配置VCLK2时钟为37.5MHZ

使能N2HET1-16产生频率为1KHZ的频率

使能N2HET1-16的引脚

测试到pwm