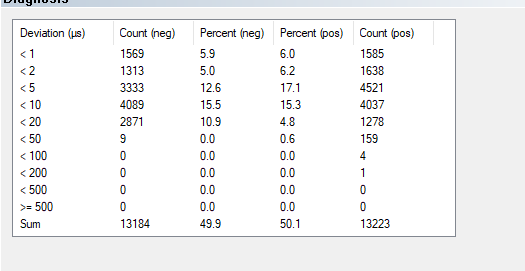

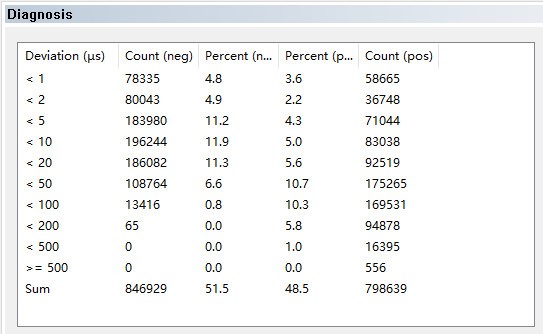

各位专家好,我在使用Beckhoff SCC Demo时,采用FreeRTOS任务,模拟PDI和Syn0中断,视乎可以实现EtherCAT的DC功能,但感觉DC功能并不真实,1C32/1C33.20的Sync Error,有错误,且DC同步抖动非常大,基本都大于500us。

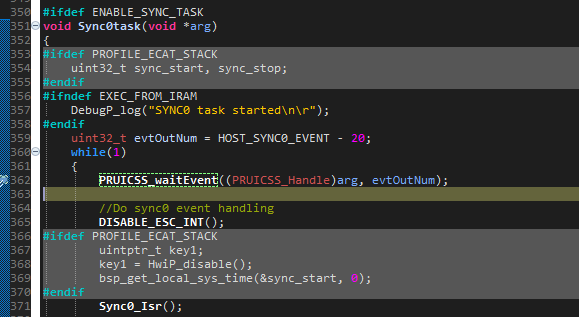

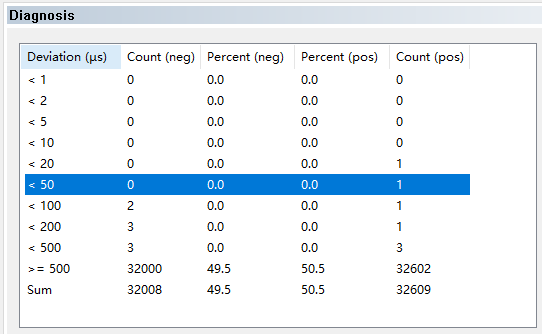

然后我换成真实的PDI和Syn0中断,发现,在DC同步模式下,PDI中断可以连续出现,而Syn0中断,只出现了一次,就没有再出现了,请问这是怎么回事,如何才能让Syn0中断,连续出现?

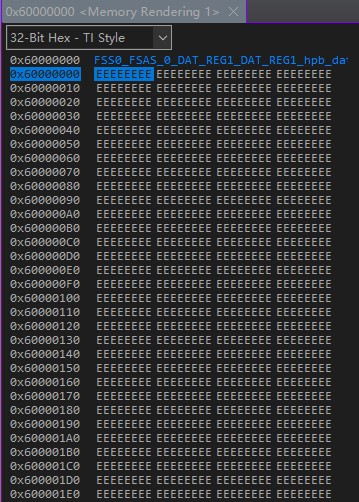

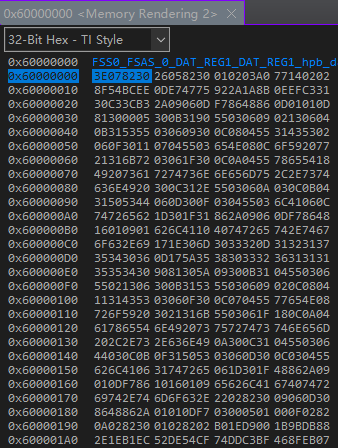

另外,在使用DC功能时,我连续监视EtherCAT的0x0910的DC系统时钟,发现此时钟,在刚开始,可以和TwinCAT的PC时钟一致,但在运行10分钟后,会比PC时钟,快20秒左右,时间越长,快的越多,请问这是怎么回事?谢谢。