“UNLOCK problem with TM4C123GH6M PF0 Pin”

I’m using PF0 pin as SSI1 RX function, but PF0 default is NMI. I write the unlock PF0 code as the example showed in forum as follows.

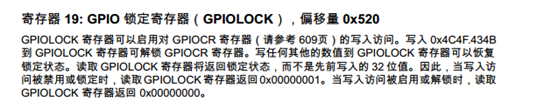

HWREG(GPIO_PORTF_BASE+GPIO_O_LOCK) = GPIO_LOCK_KEY; //Unlock

HWREG(GPIO_PORTF_BASE+GPIO_O_CR) |= 0X01; // Enable PF0 AFS

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOF); SysCtlPeripheralEnable(SYSCTL_PERIPH_SSI1); GPIOPinConfigure(GPIO_PF0_SSI1RX);

HWREG(GPIO_PORTF_BASE+GPIO_O_LOCK) =0; // Relock

It works well on the first time the program is debugged and PF0 is working as SSI1RX. But when the target board is reset or re-power on. The TM4C123G does not work and runs into a fault ISR which led to an infinite loop. After this it never works again, unless we comment the unlock program code. But if we do this, the PF0 function is default to NMI pin again.

How can I permanently set PF0 to SSI1RX function?