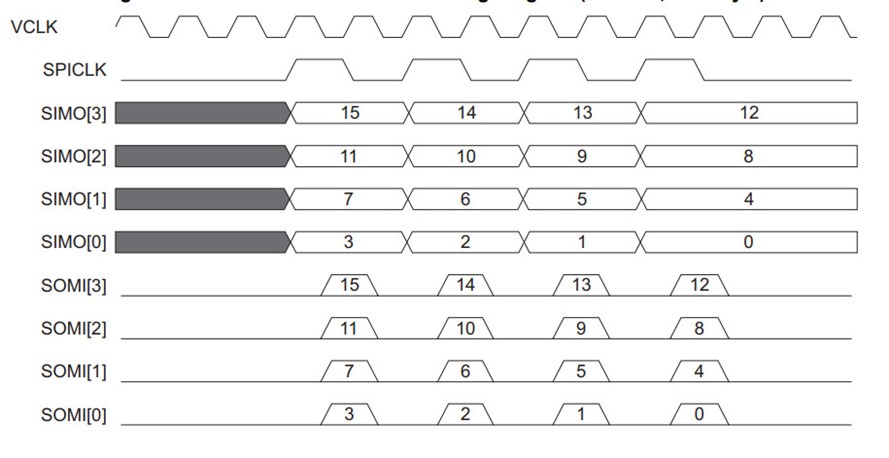

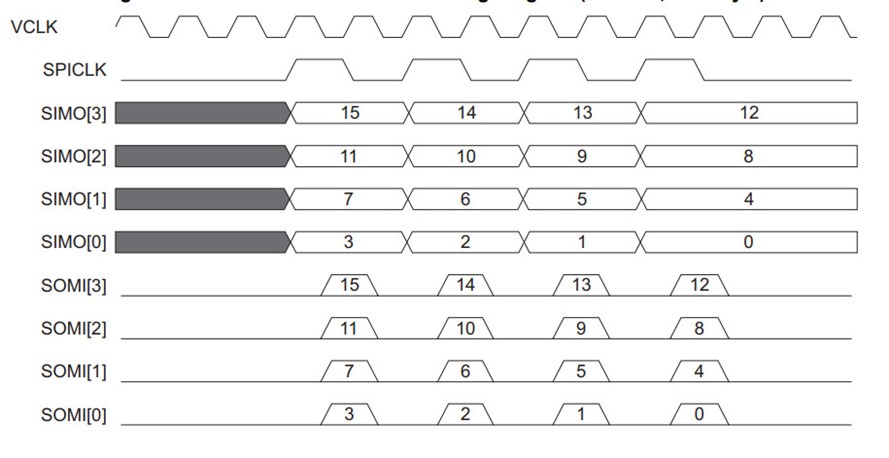

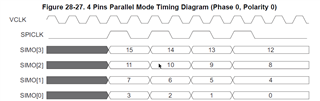

该产品MibSPI模块在4线发送16bit数据时,SIMO[3:0] 分别输出15,14,13,12,而不是发送15,11,7,3bit;请问为什么只支持这种模式,有没有办法切换到SIMO[3:0] 分别输出15,11,7,3bit信号;

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

该产品MibSPI模块在4线发送16bit数据时,SIMO[3:0] 分别输出15,14,13,12,而不是发送15,11,7,3bit;请问为什么只支持这种模式,有没有办法切换到SIMO[3:0] 分别输出15,11,7,3bit信号;

Hi,

您是说在parallel模式下,您没有像 TRM 波形一样获得输出是吗?

如果是的话,工程师这边根据 TRM 获得了波形。

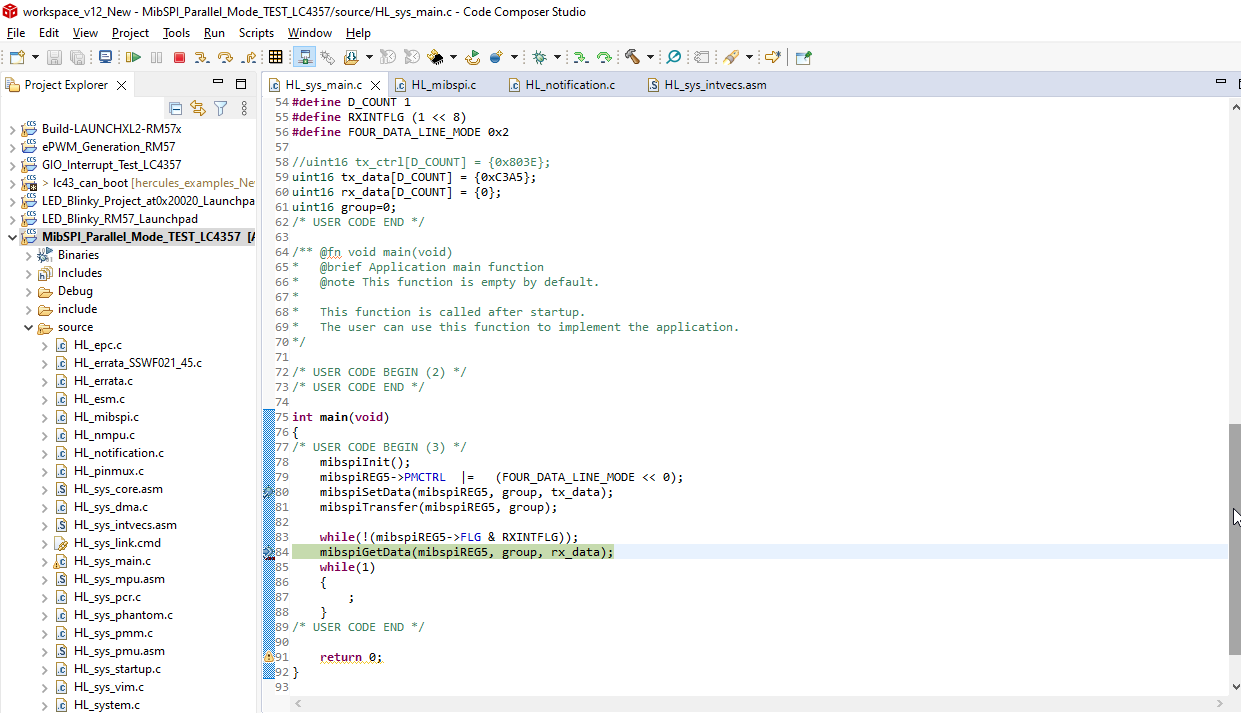

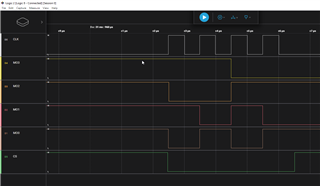

您可以看到,工程师以4 line parallel 模式发送数据0xC3A5,获得了以下输出波形:

MO3 - bit-15, bit-14, bit-13, bit-12 = (1, 1, 0, 0)

MO2 - bit-11, bit-10, bit-09, bit-08 = (0, 0, 1, 1)

MO1 - bit-07, bit-06, bit-05, bit-04 = (1, 0, 1, 0)

MO0 - bit-03, bit-02, bit-01, bit-00 = (0, 1, 0, 1)

输出与TRM中的相同:

工程师的代码也给您贴在这边,您可以参考下看看:

Thanks

Hi,

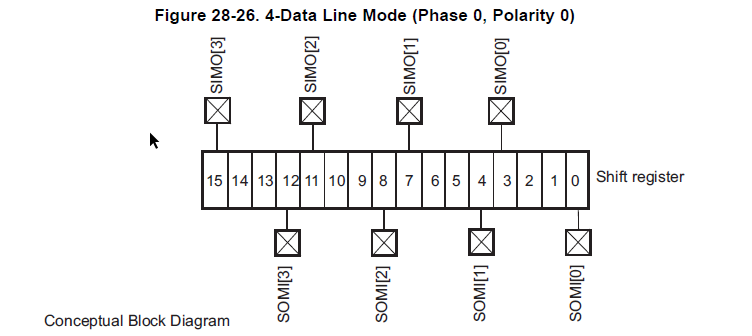

还有该器件那样输出是基于什么考虑,主要应用是什么,

我们也不太了解为何这样设置输出,我的理解是该方法较简单,可以提高吞吐量,因为

只考虑 MO3在bit 15上硬接线,MO2在bit 11上硬接线,MO1在bit 7上硬接线,MO0在bit 0上硬接线。 在第一个时钟脉冲时,bit 15将在 MO3上移出,bit 11将在 MO2上移出,bit 7将在 MO1上移出,bit 3将在 MO0右侧移出、。因此对于下一个时钟脉冲来说,可以将移位寄存器中的数据向左移动一位,除此之外没有其他动作。现在您能看到bit-14将位于 MO3上,bit-10位于 MO2上,bit-6位于 MO1上,bit-2位于 MO0上。 对于下一个时钟脉冲,数据将再次左移1且以此类推。 您可以看到该方法较简单,也是一种高吞吐量的方法。可能这就是该设计的原因。

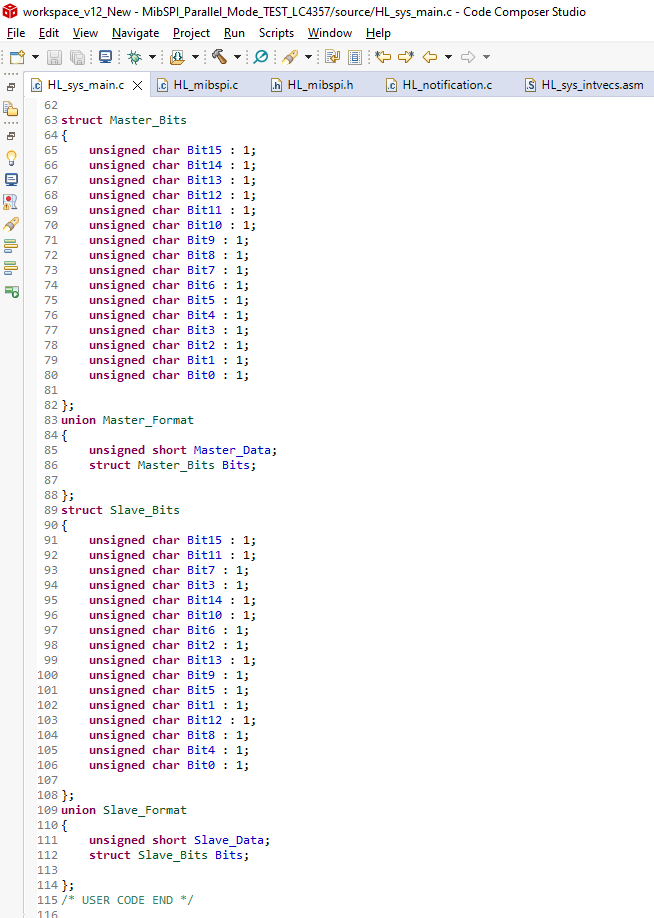

很抱歉并没有硬件机制可以来实现您的输出要求,不过我们可以在软件中实现。如果我们在向从器件发送数据之前更改bit位置,以及在从slave接收数据后更改位位置,情况会怎样。

工程师在软件中做了以下测试,来验证该方法是否成立:

1)根据主设备和从设备的顺序创建了two-bit field结构:

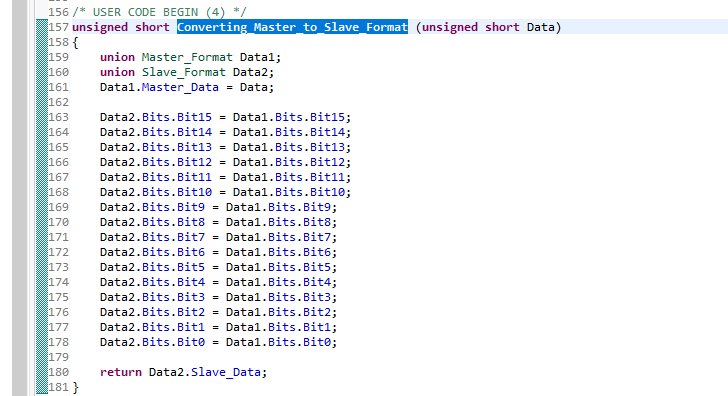

2)工程师还创建了一个“Converting_Master_to_Slave_Format" API,该 API 在向从器件发送数据时很有用,并且该 API 会在我们发送数据之前根据从器件位顺序转换主器件位顺序。

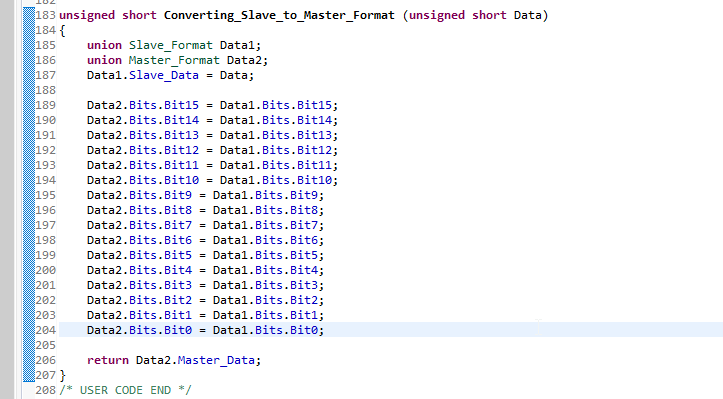

3)同样地,工程师还创建了另一个名为”Converting_Slave_to_Master_Format“的API,该 API有助于将从slave接收到的数据转换为master顺序。

不过您也可以很明显的看到,当我们需要转换每个接收或传输的数据帧时、此方法会在一定程度上降低吞吐量。 但很遗憾目前由于protocol不匹配,无法通过其他方式与从器件连接。

以下是完整项目,供您参考:

Thanks