Part Number: AM2634-Q1

1.当前R5主频为400MHZ,在手册描述中写到EPWM是属于CONTROLSS模块,那么我是否应该去配置CONTROLSS_PLL_CLK_SRC_SEL选择为DPLL_CORE_HSDIV0_CLKOUT2(400MHZ),然后PWM的分频系数为1,那么我的PWM的基频就是400MHZ吗?

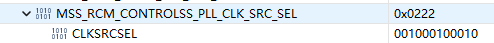

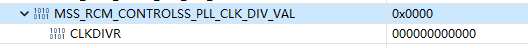

2.导入demo工程epwm_hr_duty_cycle_am263x-cc_r5fss0-0_nortos_ti-arm-clang,出来的PWM周期为1ms,1Khz,然后分频系数DIV是4,updowm模式计数是25000,那么我反推算PWM的输入时钟应为200MHZ,debug时CONTROLSS时钟配置如图

,从寄存器配置看CONTROLSS时钟为400MHZ,为何反推算时200MHZ?我看到SYS_CLK为200MHZ,PWM输入时钟是SYS_CLK吗?

,从寄存器配置看CONTROLSS时钟为400MHZ,为何反推算时200MHZ?我看到SYS_CLK为200MHZ,PWM输入时钟是SYS_CLK吗?