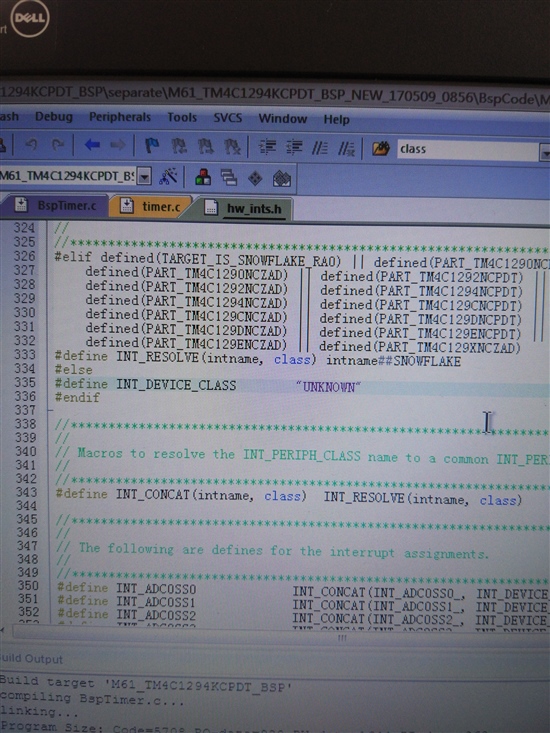

TM4C的c编程,在查看IntEnable( INT_TIMER0A )这个函数的时候,查到里面包含这样的一些宏定义:

其中的INT_TIMER0A是这么定义的:

#define INT_TIMER0A INT_CONCAT(INT_TIMER0A_, INT_DEVICE_CLASS)

这其中的符号是这么定义的:

#define INT_DEVICE_CLASS "UNKNOWN"

#define INT_CONCAT(intname, class) INT_RESOLVE(intname, class)

#define INT_RESOLVE(intname, class) intname##BLIZZARD

看不懂这里面的class关键字是做什么的?C里面有class这个关键字吗?

提前感谢了!

另外附件一句:本来像Cortex M4这样的处理直接控制寄存器什么问题不是都直接了当吗,为什么TI高了这个tivaware,有的地方写得真是晦涩难懂,

感觉已经脱离了C控制硬件的本事了,成了C的技巧游戏了!