Part Number: TMS570LS3137

你好,我使用TMS570LS3137的协处理器输出PWM波形,代码如下:

- L01 PWCNT { next=L02,hr_lr=LOW,cond_addr=L02,en_pin_action=ON,pin=20,action=PULSEHI,reg=NONE,data=0};

- L02 DJZ { next=PWM_IN_Duty1,cond_addr=L03,reg=NONE,data=0};

- L03 MOV64 { next=L04,remote=L01,en_pin_action=ON,cond_addr=L02,pin=20,comp_mode=ECMP,action=PULSEHI,reg=NONE,irq=ON,data=0};

- L04 MOV64 { next=PWM_IN_Duty1,remote=L02,en_pin_action=ON,cond_addr=L03,pin=20,comp_mode=ECMP,action=CLEAR,reg=NONE,irq=ON,data=0};

在通常情况下,这样输出的PWM是没有问题的,但是我发现如果主处理器在改变其它HET引脚的输出(如主处理器改变HET4、HET7引脚输出,协处理器通过HET20引脚输出PWM),此时输出的PWM将会不准,我使用如下一段代码进行了实验(协处理器代码不变):

- drvSetABSyn((FLOAT32)0.5, 700U);

- drvSoftwareDelaySomeMs(10000U);

- while(1)

- {

- hetREG1->DOUT &= (uint32)(~(((uint32)1U) << 4));

- hetREG1->DOUT |= ((uint32)1U) << 7;

- hetREG1->DOUT |= ((uint32)1U) << 4;

- hetREG1->DOUT &= (uint32)(~(((uint32)1U) << 7));

- }

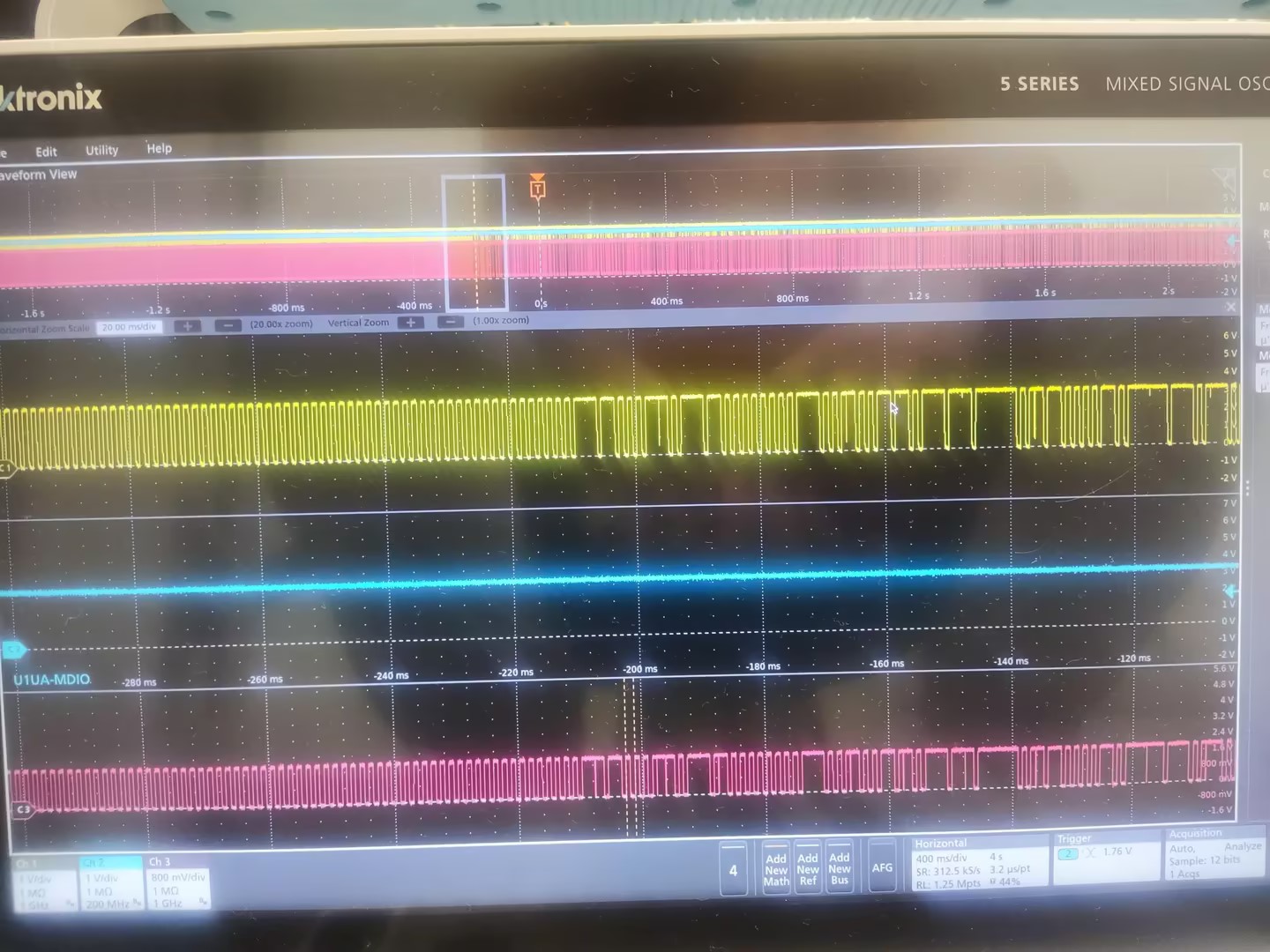

第一行通过修改协处理器的内存输出占空比为50%,频率为700HZ的PWM波形,第二行延时10秒,之后循环控制HET的第四和第七引脚。最终的输出结果如下图:

其中黄线是HET20引脚输出的PWM波形,可以明显看出,在主处理器控制HET引脚前波形是没问题的,在控制后PWM就异常了。

请问发生这个现象的原因是什么?有什么解决方法?