Part Number: BOOSTXL-DRV3245AQ1

Hi,

Due to the inability to contact your company's after-sales engineer, we can only post a request for help here.

We found a phenomenon when using DRV3245 and need your company to confirm whether it belongs to the chip characteristics.

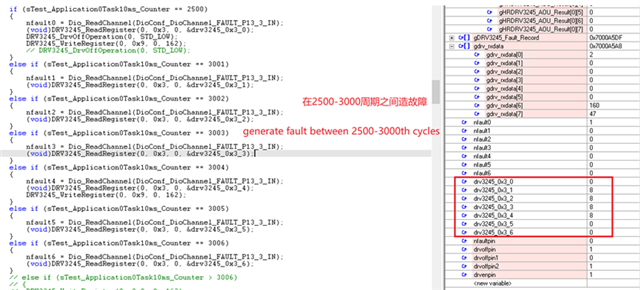

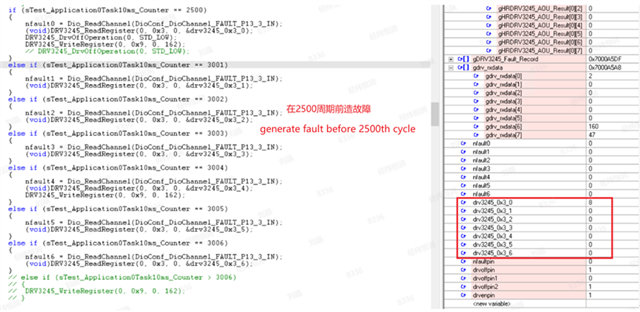

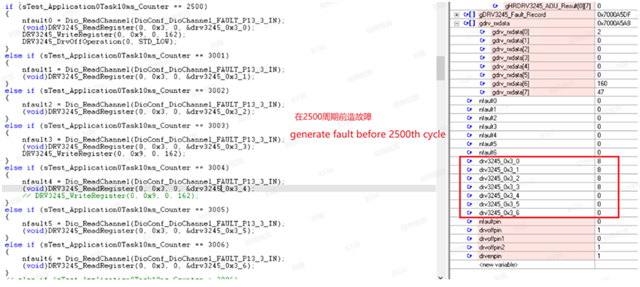

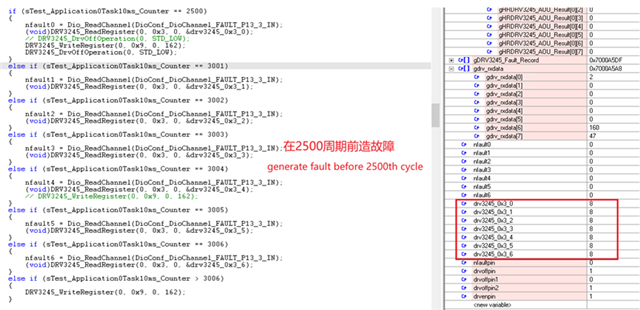

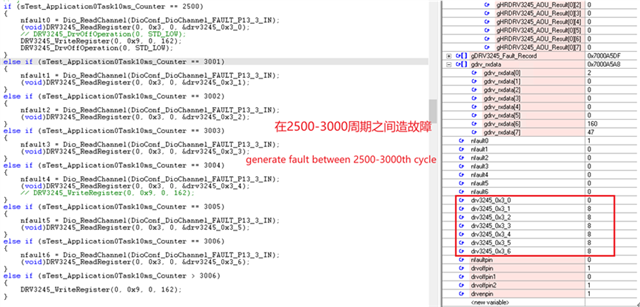

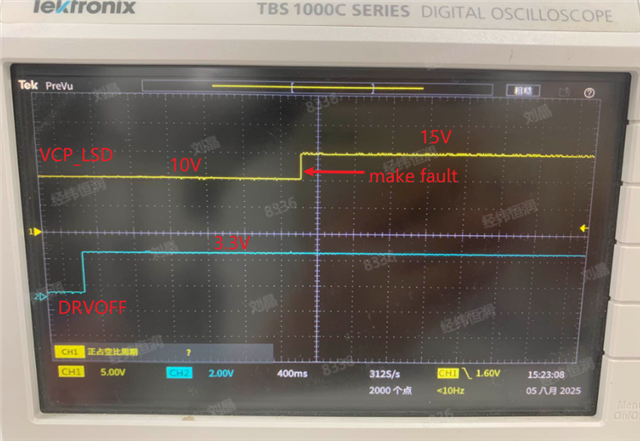

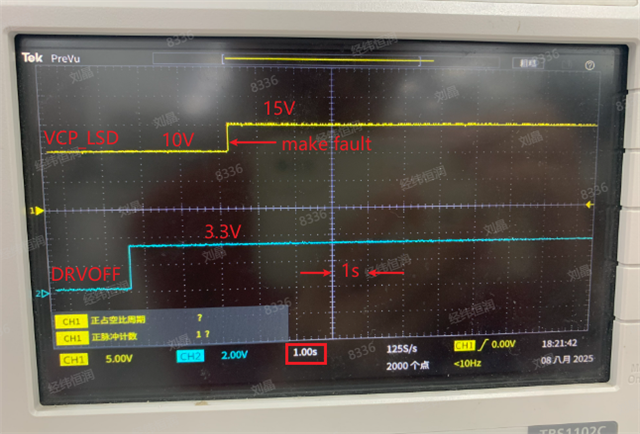

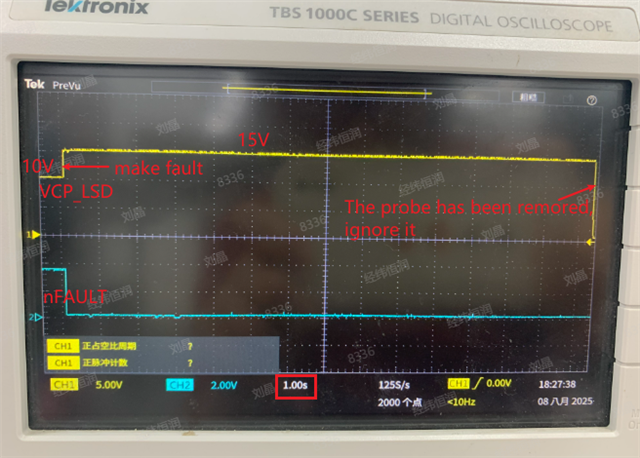

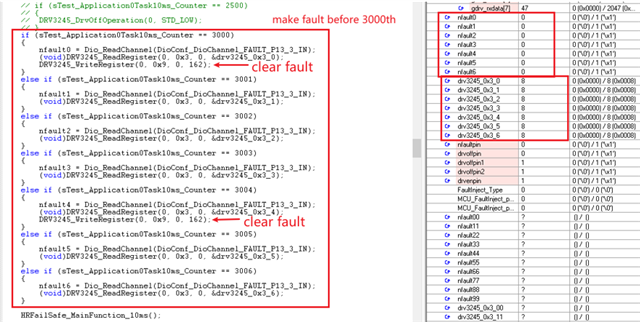

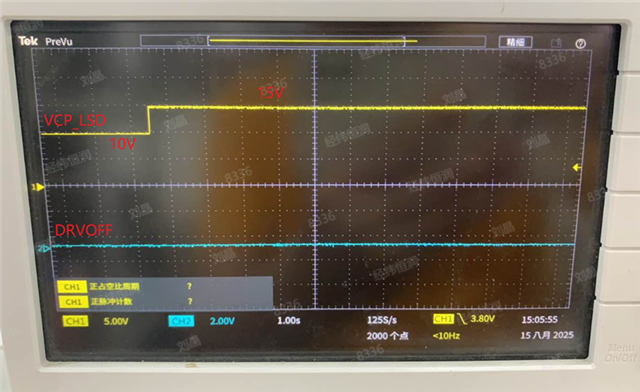

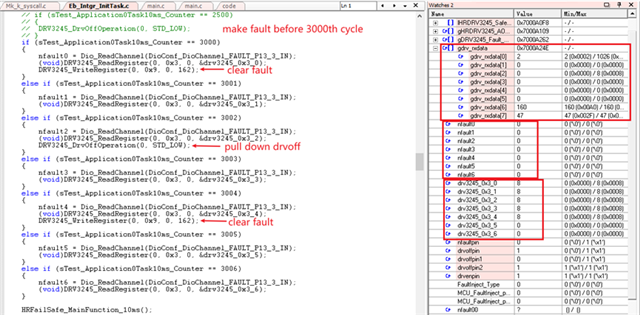

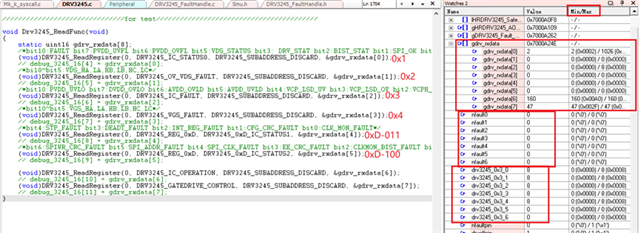

After pulling down the DRVOFF pin of DRV3245, a VLSD overvoltage fault is generated, and the fault condition persists. At this time:

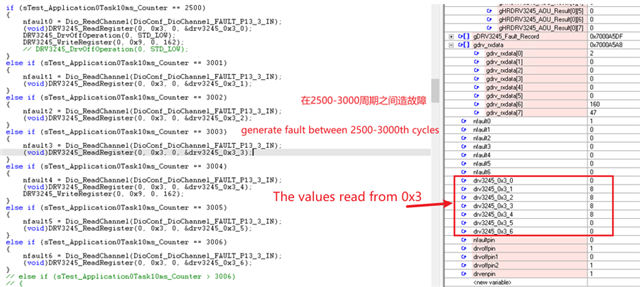

1. After the fault occurs, both the register and nFAULT can report the fault, regardless of whether DRVOFF is pulled down or which fault condition occurs first.

2. After clearing the fault once, nFAULT can report a fault, but the register cannot reset the flag position again.