Part Number: DRV8718S-Q1EVM

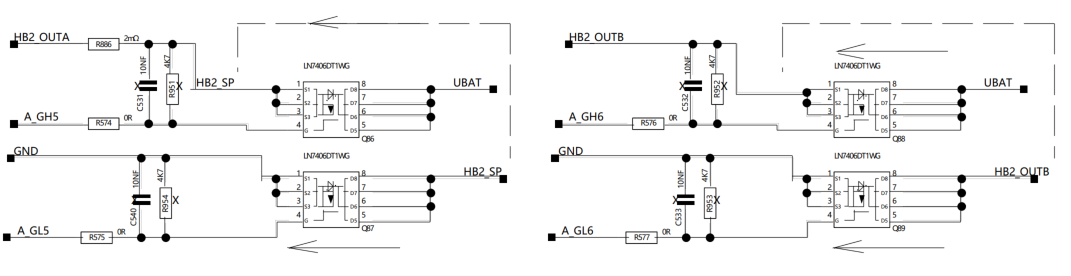

I've connected an MCU to one DRV8718 chip via SPI. The SPI configuration is: MSB first, 1MHz, CPOL=0, CPHA=1, 16bits.

I have two points of doubt, as follows:

1. I'm trying to read the IC_STAT2 Register (Address = 5h) only, the received data is 0xC002. This means that the SCLK_FLT has malfunctioned. However, the number of SCLK pulses in this frame are equal to 16. The waveform graph is as follows, What is going on?

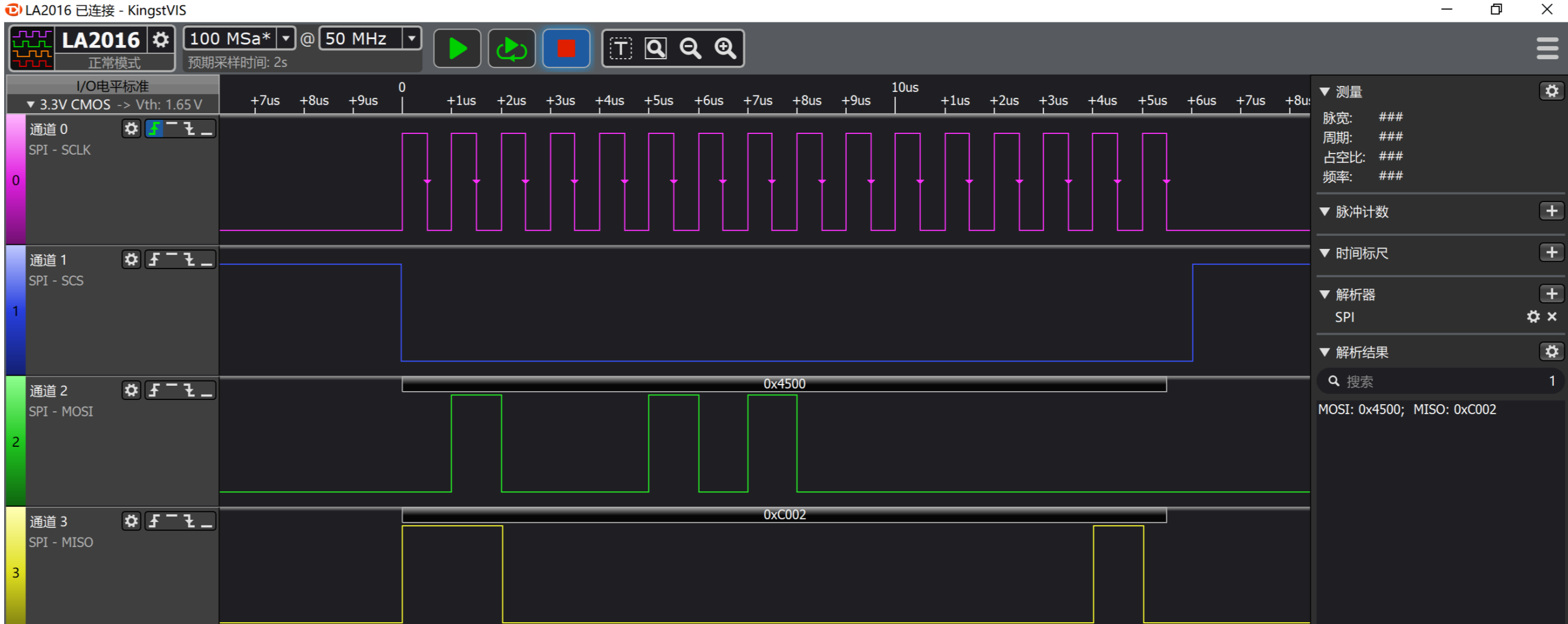

2. To control individual high-side(GH5) and low-side(GL6) external MOSFETs, I'm trying to write 0x90 into the BRG_CTRL2 register(Address = Ah), but the peripheral circuit did not functioning properly.

2. To control individual high-side(GH5) and low-side(GL6) external MOSFETs, I'm trying to write 0x90 into the BRG_CTRL2 register(Address = Ah), but the peripheral circuit did not functioning properly.Are there any other registers that need to be configured? The peripheral circuit is shown as following: