Part Number: DRV8334

通信正常:

SPI 读写测试寄存器 (0x36) 成功,证明通信链路无误。

读取其他状态寄存器 (0x12 - 0x17) 正常,所有故障位(包括 GVDD_UV, PVDD_UV, DRVOFF_FLT)均为 0 (无故障)。

硬件引脚实测 (万用表/示波器确认):

DRVOFF (Pin 9): 持续保持 低电平 (< 0.4V)。

nSLEEP (Pin 21): 保持 高电平 (> 2.1V)。

PVDD (Pin 31): 供电稳定 12V。

GVDD (Pin 30): 电荷泵电压建立正常,实测约为 12v且在尝试使能瞬间无明显跌落。

外围电容: CGVDD (1µF) 和 CCP_FLY (0.1µF/1µF) 已按 datasheet 焊接,容值正确。

软件逻辑与时序:

解锁操作: 已显式写入 0x1B = 0x0007 确保 LOCK 位为 011 (解锁状态),读回确认解锁成功。

上电时序: nSLEEP 拉高后,已延时 200ms (远超 datasheet 要求的 t_WAKE),确保电荷泵完全稳定。

清除故障: 使能前已执行 CLR_FLT 操作。

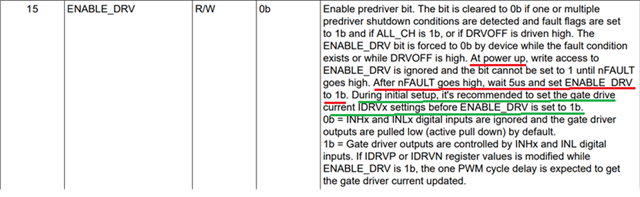

使能操作: 写入 0x1B = 0x8000 (或 0x8007),随后延时 100ms 再读回,但 ENABLE_DRV 位依然为 0。

核心矛盾点:

通常 ENABLE_DRV 写不入是因为 DRVOFF 为高、GVDD 欠压或寄存器锁定。但目前:

DRVOFF 确认为低。

GVDD 电压充足且无欠压报错。

寄存器已解锁。

没有任何故障标志被置位。

芯片仿佛在“静默”地拒绝使能命令。