Other Parts Discussed in Thread: DRV8301, DRV8353

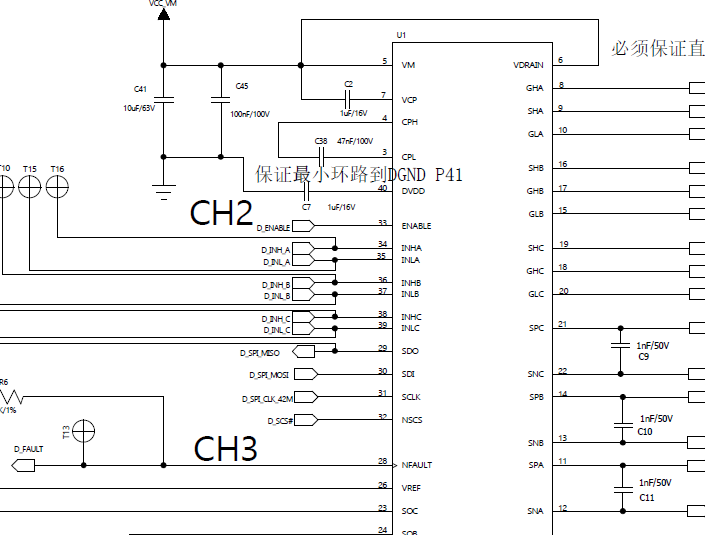

如图:VCC _VM为DC24V,NFAULT上拉电阻2.2k,在EN脚使能(拉高)时,NFAULT脚会产生一个负脉冲,造成MCU中断,通过SPI读取内部数据,并没有具体的故障位,测试图形见图2。请教可能的原因?

图1原理图 图2 测试图

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

另外一个产品在使能时没有脉冲,在使能后80ms会出现四个幅值较小的尖峰,时间间隔80ms,这个脉冲不会触发MCU中断。

好的,收到您的问题,我们会帮您反馈到英文论坛,如有答复将尽快告知您。谢谢。

较旧的器件 (如 DRV8301) 将不会有这种相同的问题。

您提供的最新图像中显示了 nFAULT Llike 或 GND 上的噪声,我们猜测该噪声可能来自电路上的其他位置。

希望以上回答对您有所帮助,如有其他问题请随时联系我们

较旧的器件 (如 DRV8301)和DRV8353这部分电路有什么区别?图2 波形已经影响功能。不单单用噪声来解释吧。这种干扰问题虽然可以通过外接电容或软件滤掉,但是电容会造成故障时下降沿的传输延迟。

您好我会将您的问题反馈到英文论坛。因国庆假期来临,预计答复您的时间为下一个工作日。感谢理解!

在较新的器件中,当加电状态机在执行时,nFAULT 引脚保持低电平,并且 nFAULT 引脚在加电状态机完成后会释放。

而较旧的器件在加电序列期间不会影响 nFAULT 引脚。

我们通常使用以上方法来确定 DRV 何时通电以及nFAULT 上的上升沿指示器件何时准备好接收命令。

在较旧的器件中,您在发送命令之前必须等待 tWAKE 的最大可能持续时间,因为在器件启动完成后,我们目前没有明确的方法来判断。

软件滤波器是解决此问题的理想方法,因为当器件由于使能或加电进行加电时,您可以非常快速地忽略第一个 nFAULT 低脉冲。

希望以上回答对您有所帮助,如有其他问题请随时联系我们。