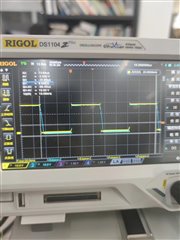

DRV8328ARUYR预驱芯片的工作状态问题,原理图是参考EVM给的图设计的,按照datasheet ,当INHx INLx 均为逻辑0时候,SHx处于高阻态。目前测试情况是:问题1:PVDD供电是24V,上电状态下,INHx INLx未给信号时候,均为低的时候,SHx对地的电压有24.44V,请问正常吗?问题2:测试时,下桥打开正常,当给打开上桥的控制信号时候,可以发现内部高侧PMOS并未导通,此时fault拉低,因为shx对地有电压,当下桥打开的时候,VBSTx已经完成自举有33V的对地电压,请问故障原因?