DRV8412自带峰值电流保护,超过峰值电流则会锁死。锁死以后必需reset才能放开。

请问一下:1、这个峰值过流保护(OC)功能是否能去掉,通过什么手段去掉,目前手册上只说可以调节电阻,改变峰值电流的大小;

2、这个峰值电流保护,电流持续多久就会触发,10ms?还是多少

3、reset进行重置的时候,reset引脚需要给一个低电平再给高电平,这个低电平至少要持续多久

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,

1、这个峰值过流保护(OC)功能是否能去掉,通过什么手段去掉,目前手册上只说可以调节电阻,改变峰值电流的大小;

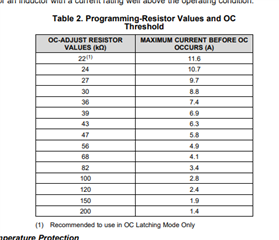

需要使用 OC_adj 电阻器来保护器件承受超出其承受能力的电流的影响。请参阅下表:

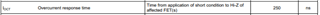

2、这个峰值电流保护,电流持续多久就会触发,10ms?还是多少

过流响应时间您可以在datasheet中的electrical characteristics部分找到:(250ns)

3、reset进行重置的时候,reset引脚需要给一个低电平再给高电平,这个低电平至少要持续多久

通过了解 PWM 频率是如何达到500kHz,可以放心地假设 RESET 引脚此时也能够捕获上升沿和下降沿。 请参阅以下部分了解更多信息:

7.3.3 Device Reset Two reset pins are provided for independent control of half-bridges A/B and C/D. When RESET_AB is asserted low, all four power-stage FETs in half-bridges A and B are forced into a high-impedance (Hi-Z) state. Likewise, asserting RESET_CD low forces all four power-stage FETs in half-bridges C and D into a high- impedance state. To accommodate bootstrap charging prior to switching start, asserting the reset inputs low enables weak pulldown of the half-bridge outputs. A rising-edge transition on reset input allows the device to resume operation after a shut-down fault. For example, when either or both half-bridge A and B have OC shutdown, a low to high transition of RESET_AB pin will clear the fault and FAULT pin; when either or both half-bridge C and D have OC shutdown, a low to high transition of RESET_CD pin will clear the fault and FAULT pin as well. When an OTSD occurs, both RESET_AB and RESET_CD need to have a low to high transition to clear the fault and FAULT signal.