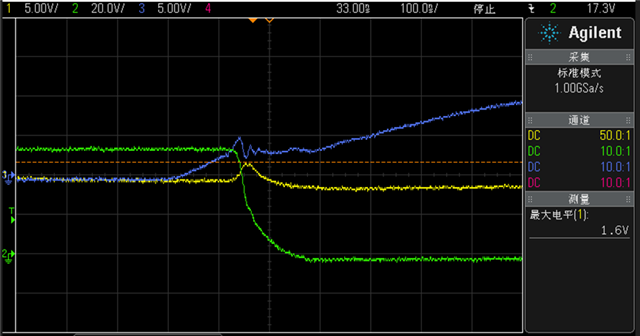

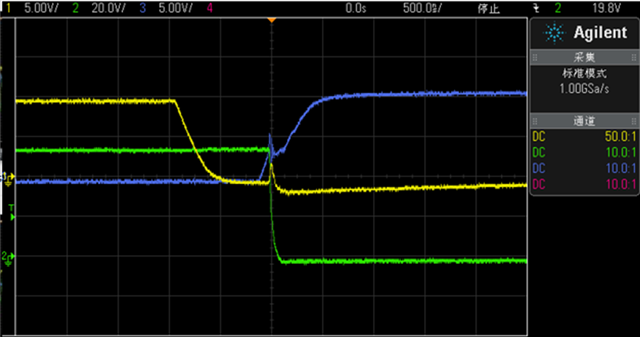

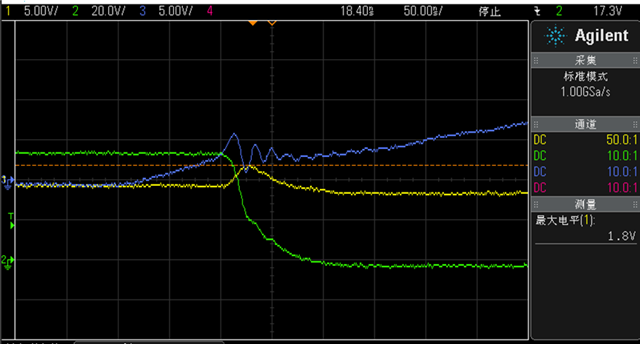

DRV8353 drive waveform testing:

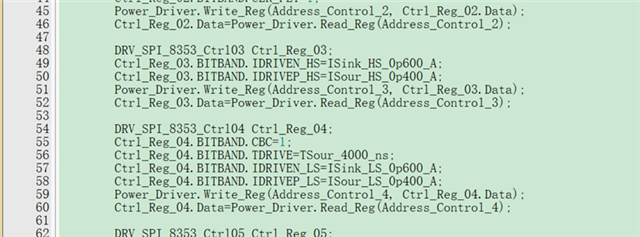

48V, PWM 20KHZ, dual mosfet, sink 600ma,source 400ma , Dead-time200ns

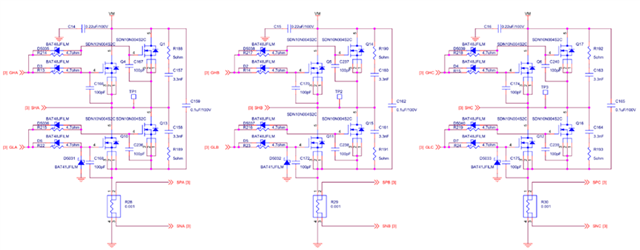

The schematic diagram is as follows:

1-channel (yellow) GHC-SHC, upper bridge VGS voltage

2-channel (green) SHC, phase voltage

3-channel (blue) GLC, lower bridge VGS voltage

The lower bridge VGS has oscillations with a significant amplitude, and the upper bridge also experiences voltage rise. Is it reasonable or does it have hidden dangers. I tried to suppress the amplitude of the oscillation:

1)100K resistors are connected in parallel between VGS, without significant changes

2)Reduce the driving current, sink 300ma source 300ma ,The falling edge slows down, but the shaking still exists, and the shaking amplitude should be lower

3)Increase the driving current, sink 800ma source 550ma ,The edge shakes more, but the shaking still increases

4)The driving current remains unchanged (sink 600mA source 400mA), and without 100pF between GS and 100K pull-down resistor, the oscillation increases slightly

5)Adjust the driving current (sink 600mA source 300mA) and add 100pF. Without 100K pull-down, the oscillation increases slightly ,Is this OK?