Part Number: BQ25713B

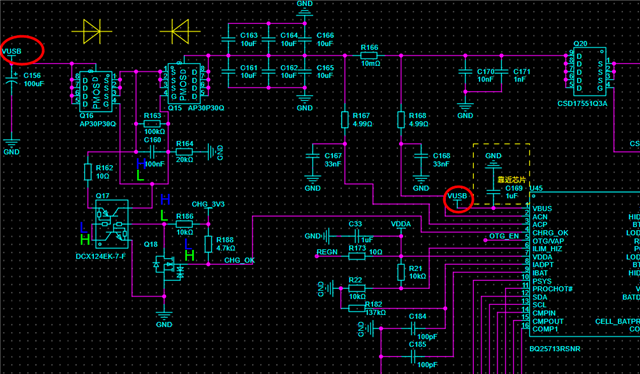

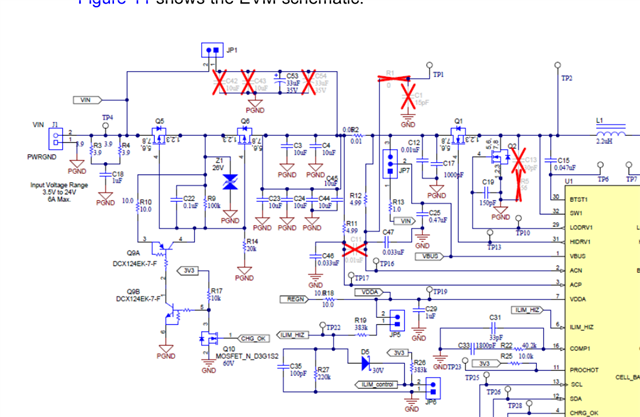

你好,当我参考EVM的原理图,启用浪涌电路设计电路时,我的OTG无法输出,寄存器会报OTG UVP错误,输出电压似乎是靠VBUS采集调节的,而因为类似EVM上的Q5,6导致电压不能到Vin,而输出开环,是这样吗?可以帮忙在EVM上测试一下吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好

,当我参考EVM的原理图,启用浪涌电路设计电路时,我的OTG无法输出,寄存器会报OTG UVP错误,输出电压似乎是靠VBUS采集调节的,而因为类似EVM上的Q5,6导致电压不能到Vin,而输出开环,是这样吗?可以帮忙在EVM上测试一下吗?

是的、仅当 CHG_OK 信号为高电平时、Q5/Q6才会导通。 仅当存在有效适配器时、CHG_OK 信号才会变为高电平。 因此在 OTG 模式下、CHG_OK 将为低电平、Q5/Q6不会开启。

可能的权变措施:

使用 MCU 或类似器件驱动 Q10 MOSFET。

使用跳线(类似于 EVM 原理图中的 JP1)绕过 Q5/Q6。