设计50W,3.5A BUCK 电源,输出电流达到2.2A以上时,芯片HO和LO引脚驱动出现异常,随着输出电流的增加,输出电压开始下降(没有到达限流值),考虑是干扰引起。对BUCK电源进行重新布局设计。

请TI工程师帮忙确认是否可行。3073.DPS5024-015-NISO电路板.pdf

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

设计50W,3.5A BUCK 电源,输出电流达到2.2A以上时,芯片HO和LO引脚驱动出现异常,随着输出电流的增加,输出电压开始下降(没有到达限流值),考虑是干扰引起。对BUCK电源进行重新布局设计。

请TI工程师帮忙确认是否可行。3073.DPS5024-015-NISO电路板.pdf

LM5148: 主MOSFET关断后出现短时驱动脉冲(非开关周期的下一个脉冲) - 电源管理论坛 - 电源管理 - E2E 设计支持

这个之前就有讨论过,TI工程师分析是布局存在问题。所以我重新进行PCB设计,TI工程师让我重新发的帖子。您先看一下前面这个帖子的信息,有需要我补充的,我再发给您。

至于布局。这是双层板吗?,由于不理想,这将是一个具有很高问题风险的挑战。如果您想继续,请在下面提供反馈。

1.很难辨认,你能为我强调HO和SW在HS MOSFET上的布线是不同的吗?

2.建议不要尝试实施这两种方案,因为它会挤占当前的感测反馈组件。建议使用RSENSE,并将RC放在引脚旁边,再次删除L2和L3。

3.将VCC GND直接连接到PGND引脚。

4.将电感器靠近HS和LS MOSFET,并保持开关节点较小。

5.确保HS和LS MOSFET尽可能靠近放置。

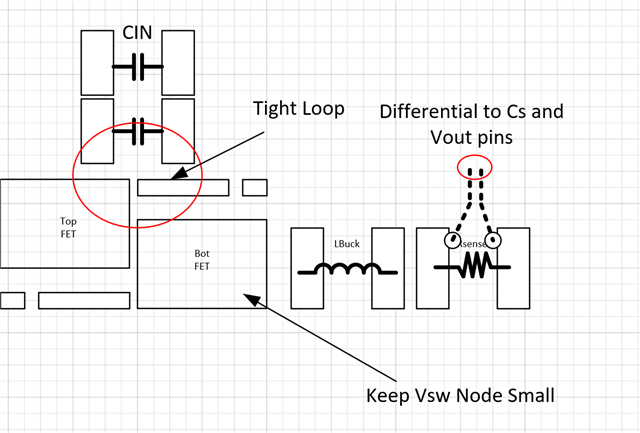

鉴于这是一个双层电路板,建议采用以下MOSFET布局。-请注意,我是如何旋转MOSFET并用输入帽封端的,而不是依赖于一个坚固的GND平面,因为我相信你只有两层。如果您有两个以上的层,可以按照所示使用。

8132.DPS5024-015-NISO电路板.pdf2364.DPS5024-015-NISO原理图.pdf

设计文档已根据建议修改,请看一下是否妥当!

栅极驱动线中不应存在电感。请注意遵循上述第2点中的建议。

参见上文。我还将使用更多的过孔将输入帽的GND连接到MOSFET的GND。您只在MOSFET侧使用了3个通孔。在双层PCB上布线具有更高的风险和挑战,需要确保有一个低Z路径,通过使用大量通孔确保高di/dt路径通过低阻抗连接。

建议你把Q1和Q2夹在一起,这样输入电容就在FET之前。

https://e2e.ti.com/cfs-file/__key/communityserver-discussions-components-files/1044/0207.Capture.JPG

您可以采用这种方法,如下所示。

这是一个概念,通过这种方式,你可以正确地定位Lo和Ho,这样你就不必将VSW与Lo轨迹交叉,