Hi TI Team!

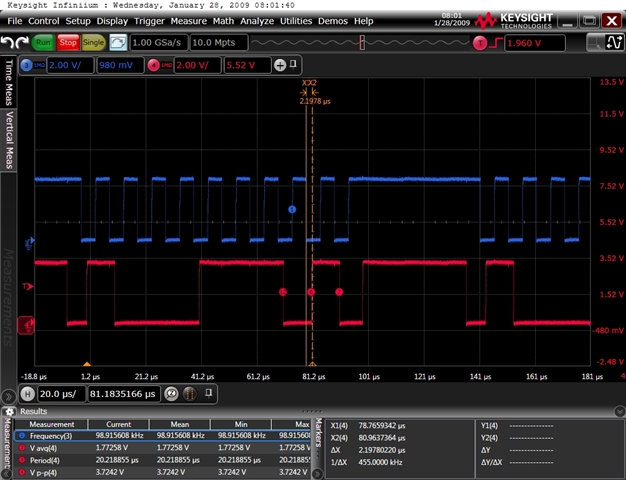

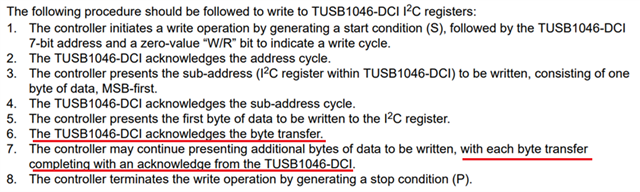

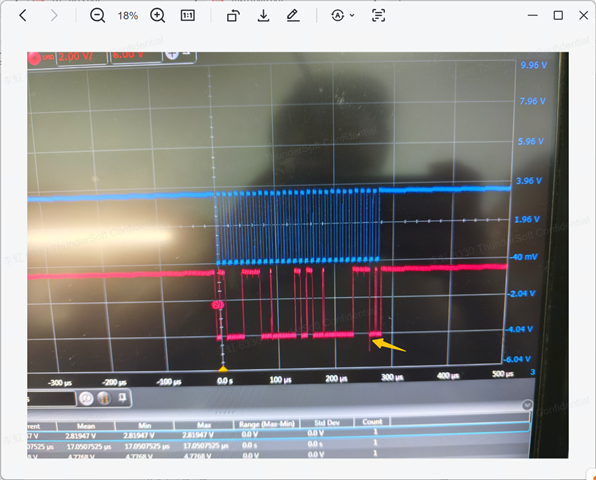

We use CYPD3125 as the master device and TUSB1046 as the slave device. We use I2C communication. When the last bit of a byte is 1, TUSB1046 will immediately pull down SDA to respond after the 8th CLK transition. When both CLK and SDA have the same falling edge, it causes a significant negative voltage overshoot on CLK and SDA.

Disconnect the I2C connection of TUSB1046. After CYPD3125 writes the 8th bit of a byte, 2 us after the 8th CLK falling edge, the SDA bus is released. Therefore, when communicating normally with TUSB1046, after writing the 8th bit, the SDA bus has not been released yet. TUSB1046 then pulls down the SDA, causing the CLK and SDA to drop almost simultaneously at the falling edge. How can this problem be solved?