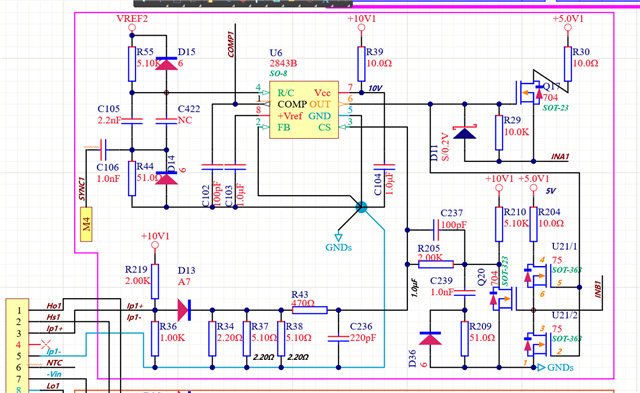

Part Number: UC2842A

Other Parts Discussed in Thread: UC2842

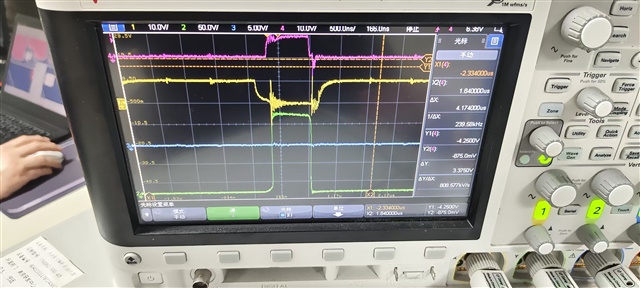

请教下工程师,这个电路是模拟恒流源电感电流采样反馈的闭环电路,恒流源功率拓扑采用同步BUCK,目前存在电流精度与SW节点震荡问题,请问下电路存在哪些问题?PWM芯片使用的UC2842,输出互补PWM,电感电流采用B82801B0205A100输出IP+、IP-信号,关键之处在于:1.电感电流信号到CS端的调理电路?;2.输出互补PWM电路与采样电路有RC耦合?

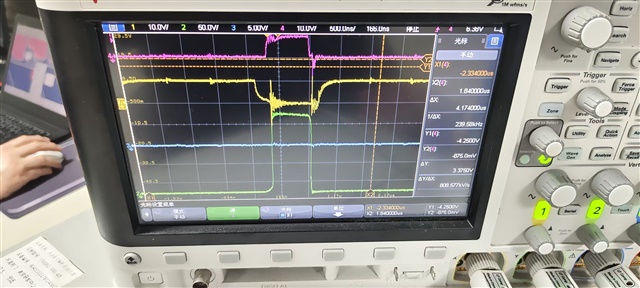

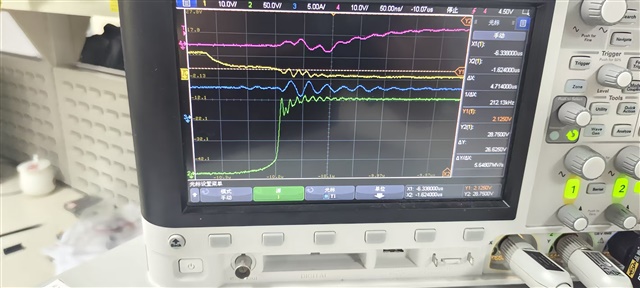

参考波形:1.紫色波形为半桥上管驱动VGS

1.黄色波形为半桥下管驱动VGS

1.蓝色波形为输出电流波形

1.绿色波形为半桥开关节点SW波形

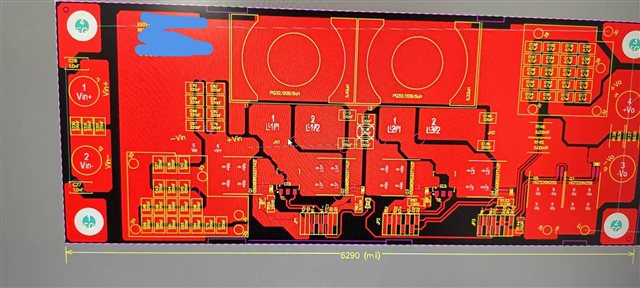

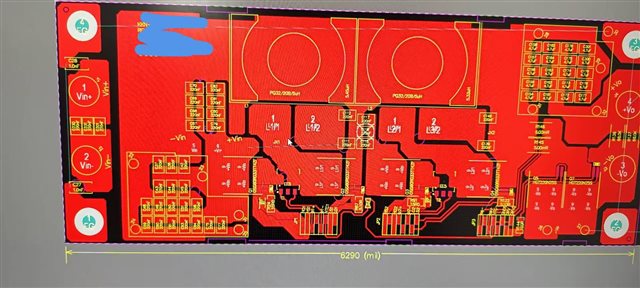

图2:

图2:

图2:

图2: