Part Number: TPS65224-Q1

Hello Ti Team:

During the testing phase, I encountered two issues that require resolution, and I would appreciate your assistance in addressing them.

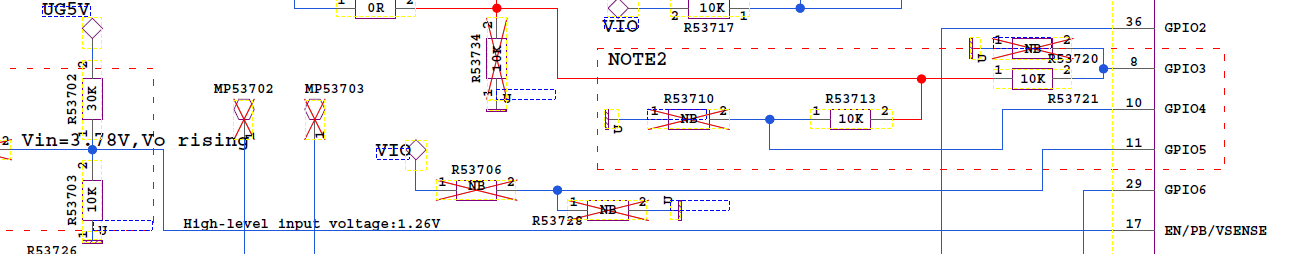

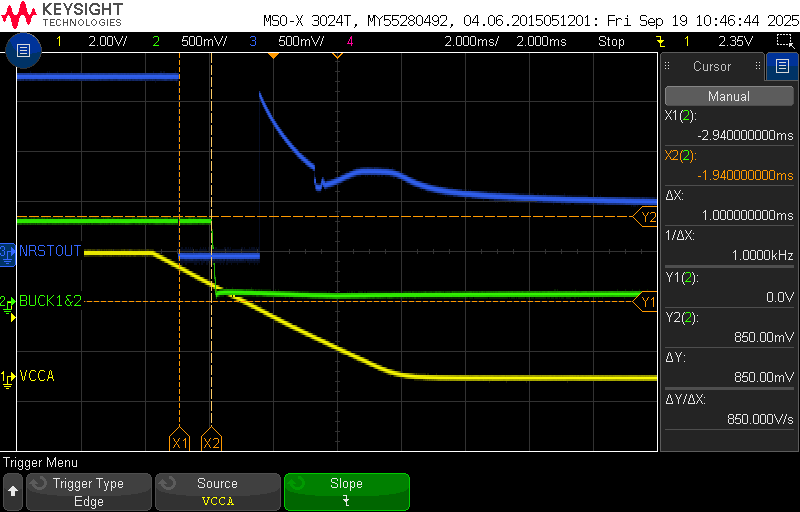

1)During the power-down sequence of VCCA, the NRSTOUT signal initially transitions to a logic low level, followed by a transient voltage spike and a gradual power-off decay. This behavior is illustrated in the figure below. Could you please provide an explanation for this phenomenon?

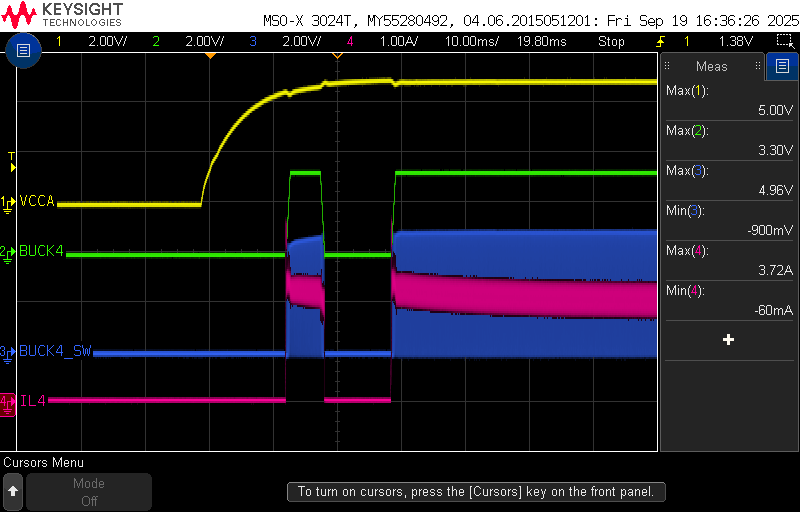

2)When Buck4 is in the output state, if an electronic load is initially used to draw a current of 2 A and the chip is subsequently powered on abruptly, a phenomenon resembling a secondary power-up event may occur, as illustrated in the figure below. Could you please clarify the underlying cause of this behavior?

Thanks!

Best Regards!