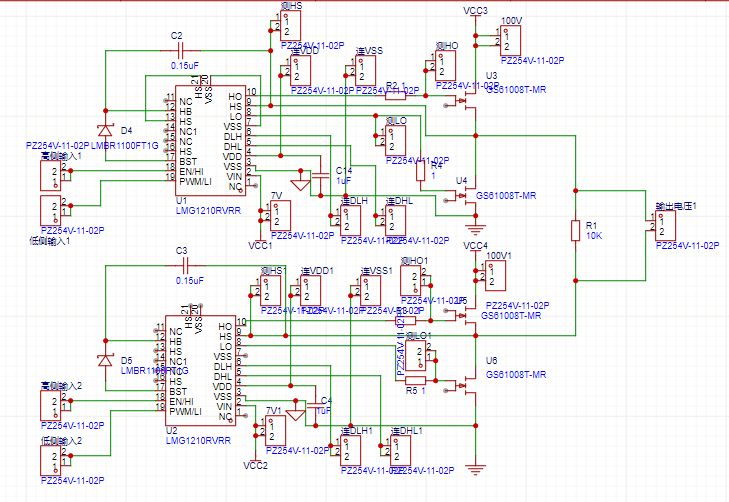

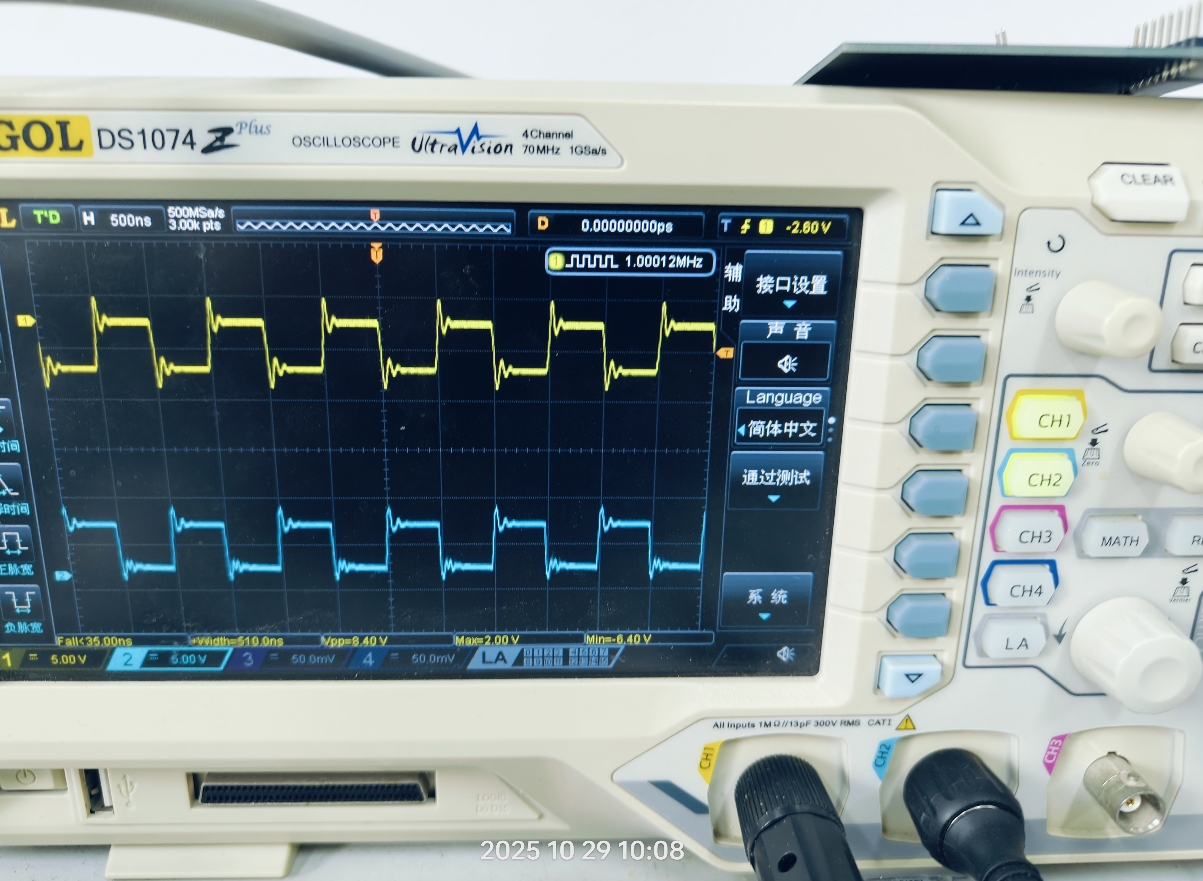

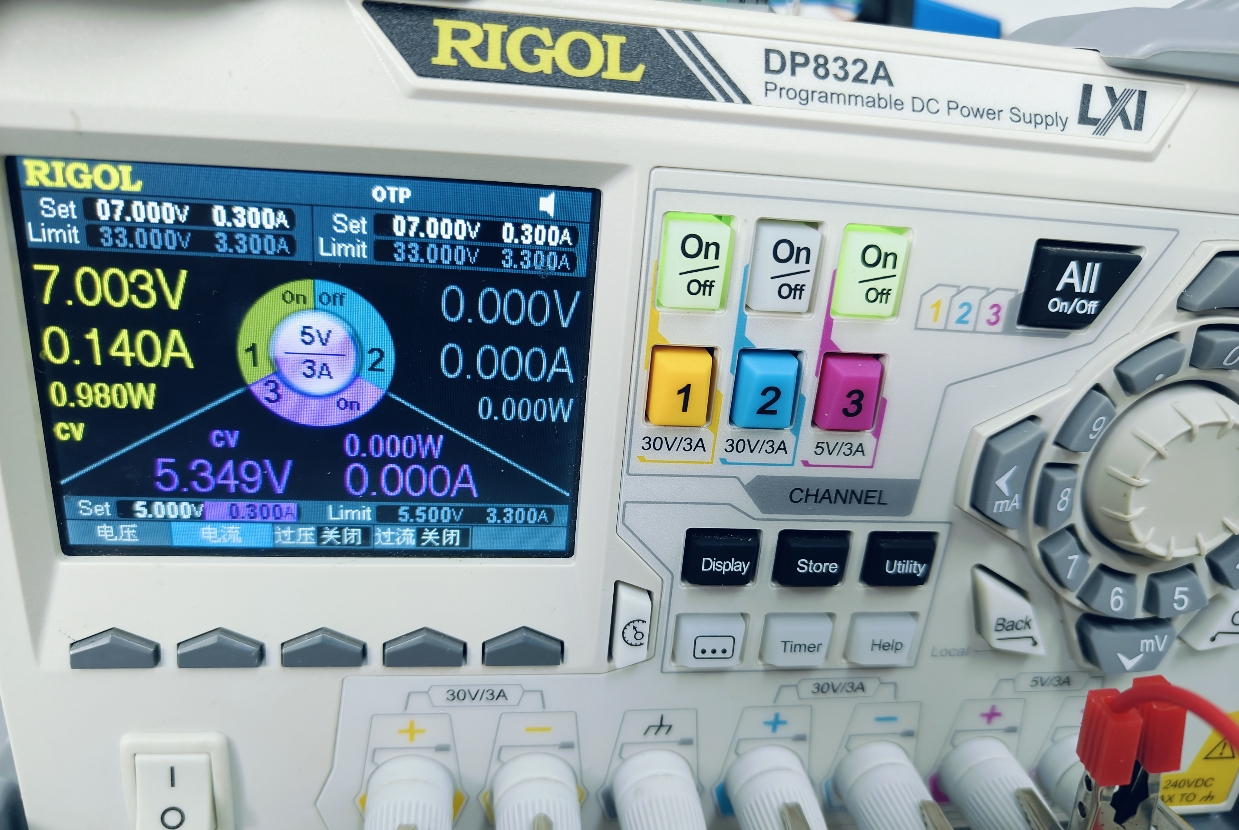

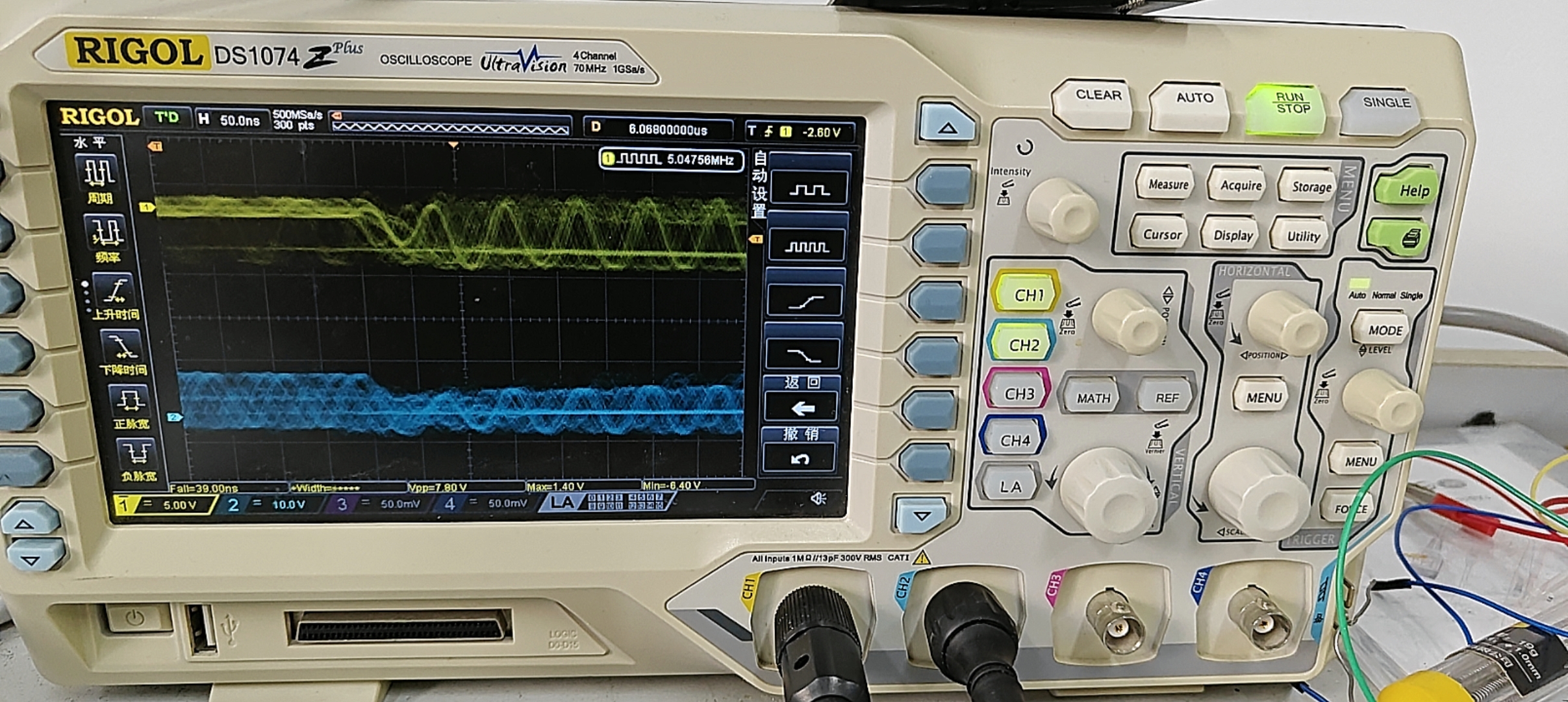

The first image shows the circuit schematic I am using. For this chip, I have chosen the IIM mode. The input signal is a pair of complementary 1MHz PWM signals generated by an FPGA. I encountered an issue: when I power only the first chip (U1) and leave U2 unpowered, the HO-HS and LO ports of the first chip (U1) show normal output, as shown in the second image. The third image shows the power generator settings and the current at that moment.

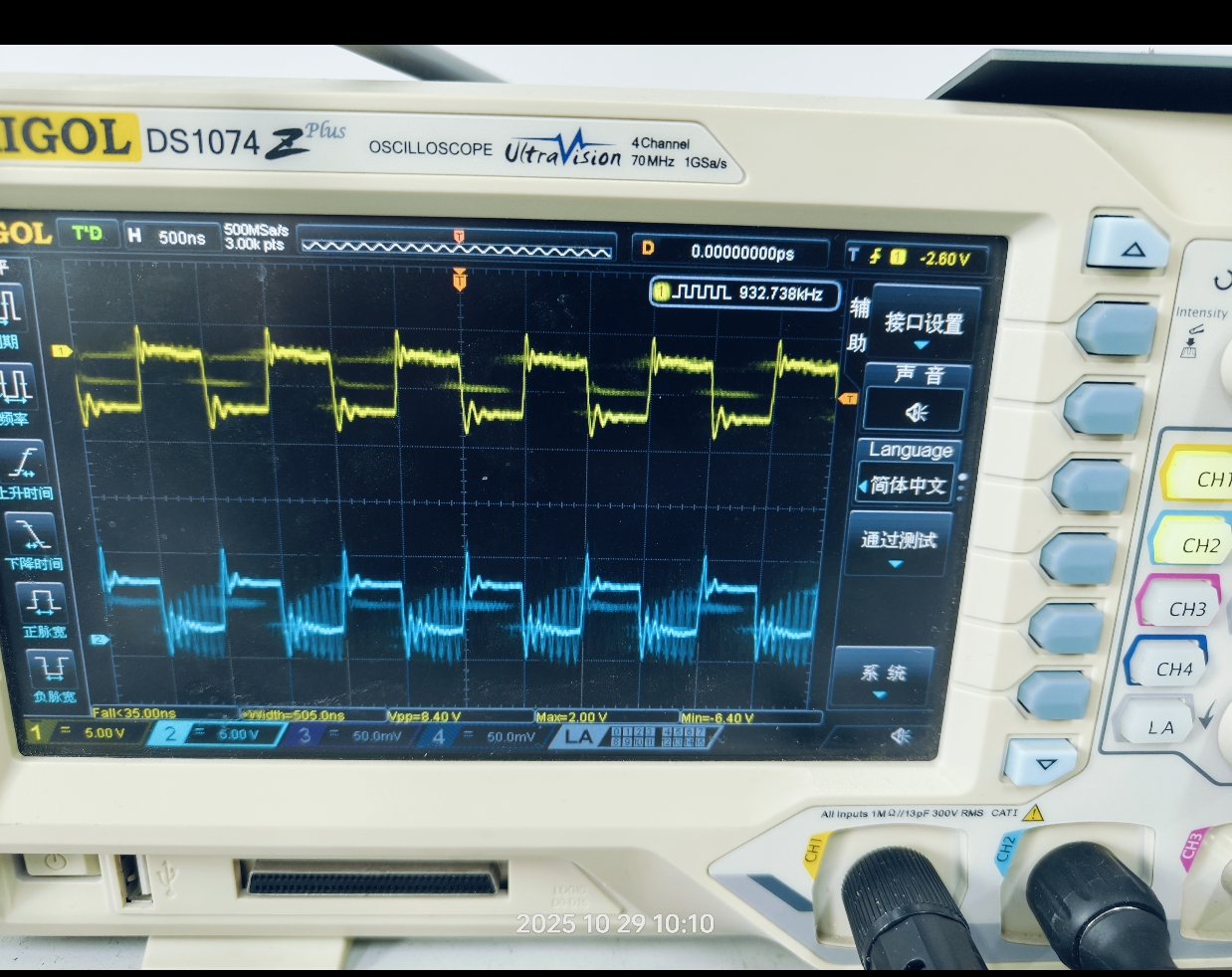

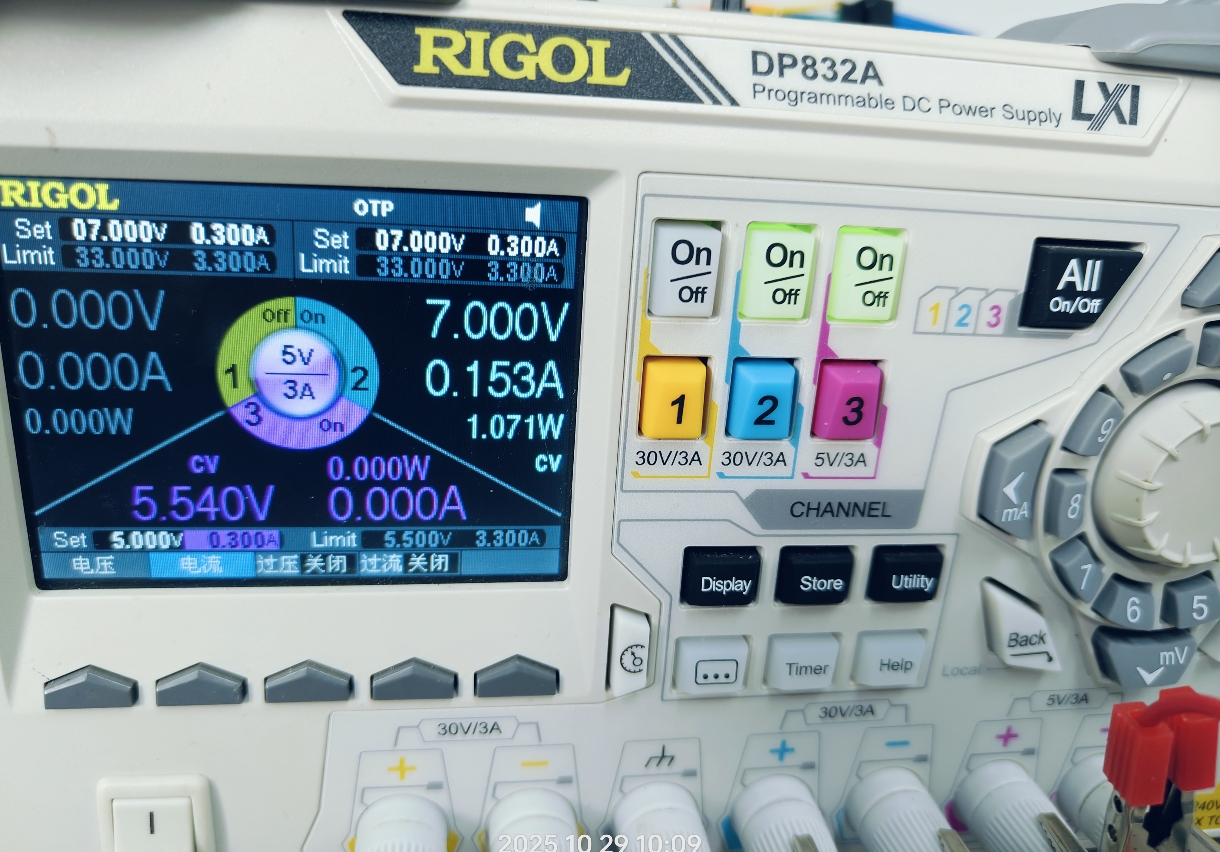

However, when I power only the second chip (U2) and leave U1 unpowered, the HO-HS and LO ports of the second chip (U2) exhibit distortion, as shown in the fourth image. The fifth image shows the power generator settings and current at this point.

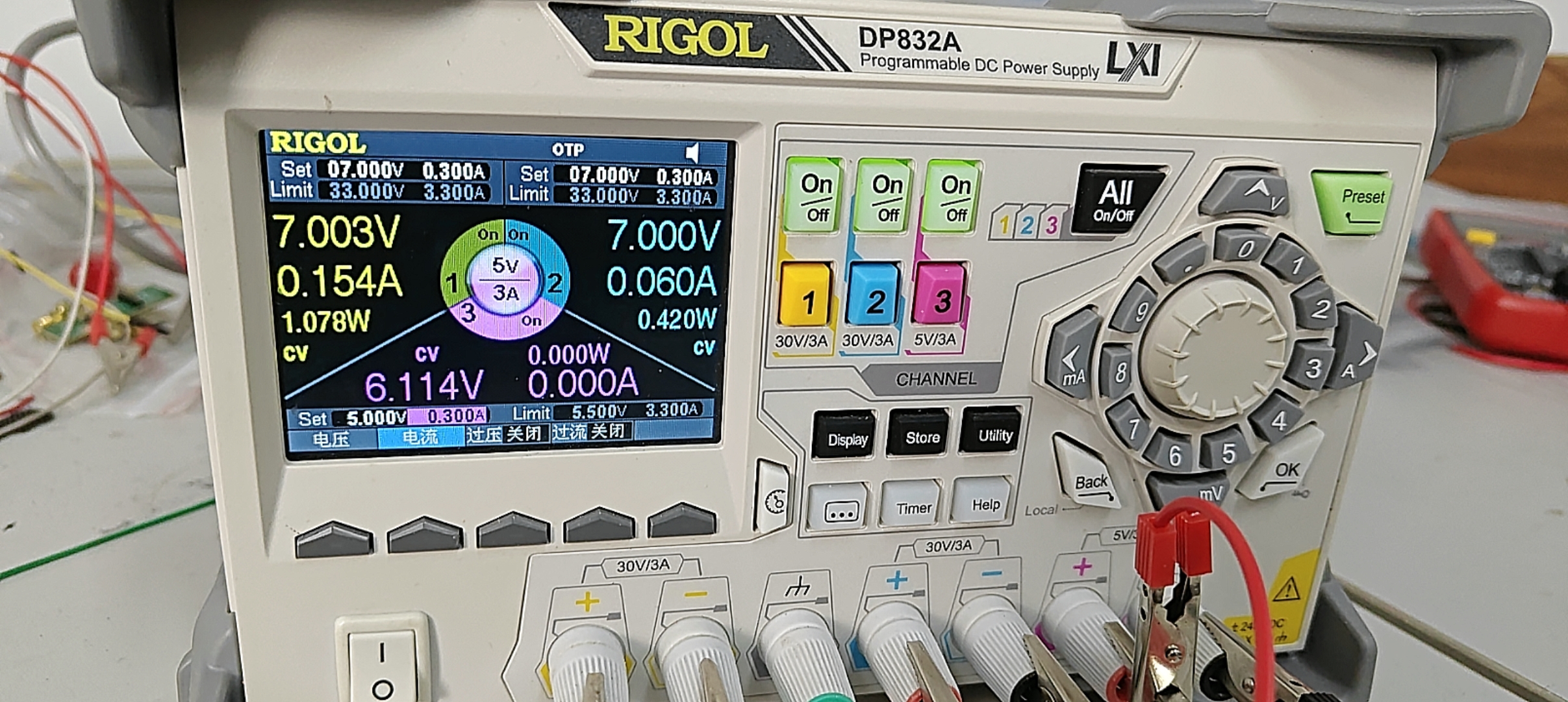

When I power both chips simultaneously, no signal is observed, as shown in the seventh image. The settings and current of the power generator at that moment are shown in the sixth image.

At present, I have no clue on how to resolve this issue. Could you provide some troubleshooting suggestions?