Part Number: TLC5954

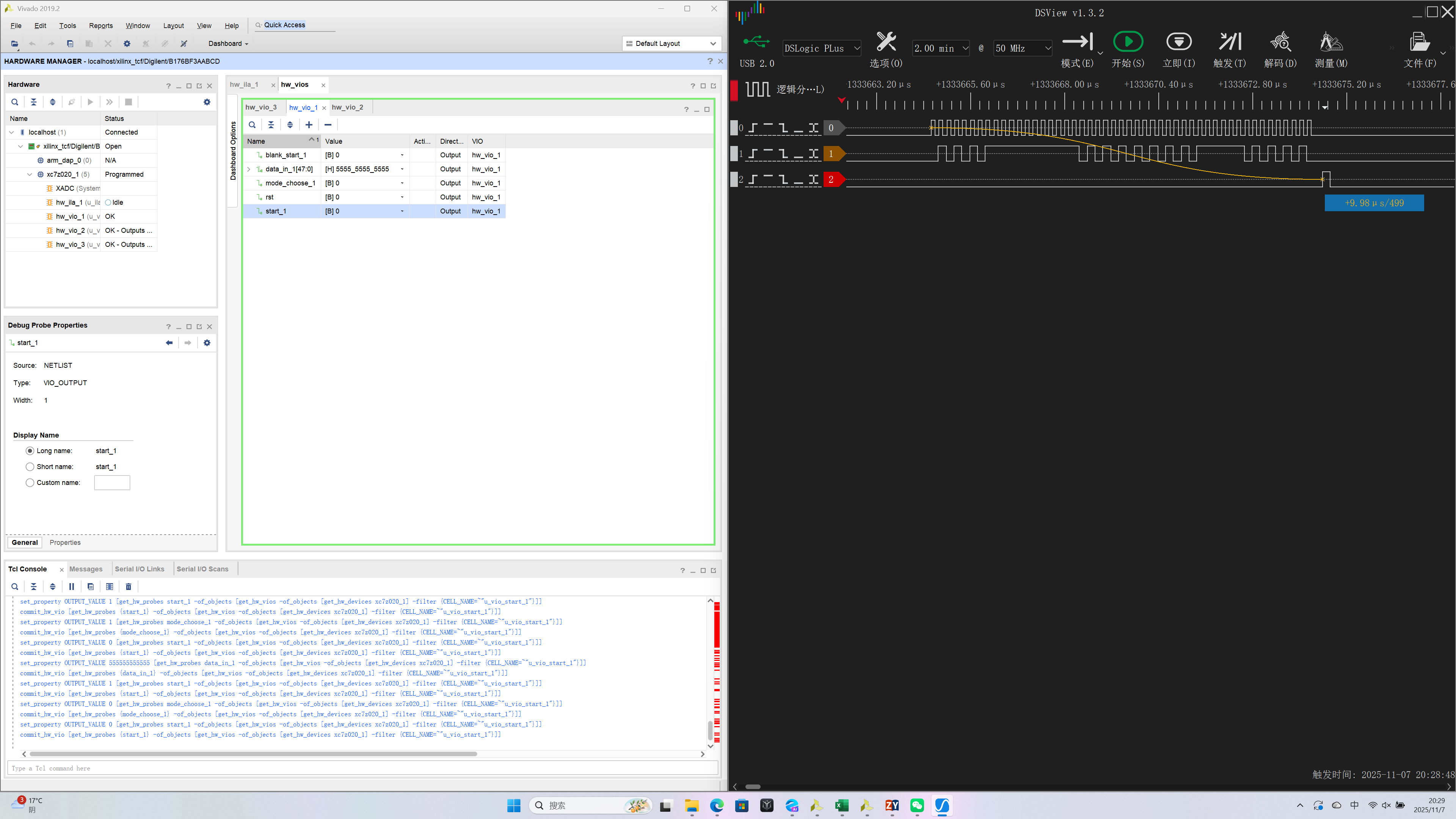

通过fpga对tlc5954芯片做驱动,使用的时钟是5M。fpga与驱动板通过四个引脚连接,sclk,sin,lat,blank

;其中blank始终拉低,现在fpga bit流下载后做驱动,根据协议把信号灌进去后,发现只有sout信号有输出,输出与sin输入一致,其余48个引脚均未拉高。有无大佬指导下问题在哪。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,

我们不是FPGA专家,只能基于TLC5954时序进行支持,请重新确认下面信息:

TLC5954初始上电后, ON OR OFF CONTROL DATA 默认为0;根据Table 6 MC默认000b; PSMODE 11b(always in Power-save mode).

如果您想使用Power-Save Mode,请将 PSMODE设置为01b 10b (FC数据写入)

根据数据手册 Figure24,一次完整的写入,需要49个SCLK时钟。

SCLK上升沿获取SIN数据,第一个SCLK上升沿时,SIN为低用于指示输出数据,由 LAT上升沿锁存到OUTXn。