Part Number: LM5100A

你好,

在单板测试LM5100AMRX芯片引脚应力,发现在芯片输出LO-VSS和HO-HS波形均有负向电压应力较(-5.3V,300KHz),超出芯片规格要求的0.3V。想咨询一下这个会有什么危害?

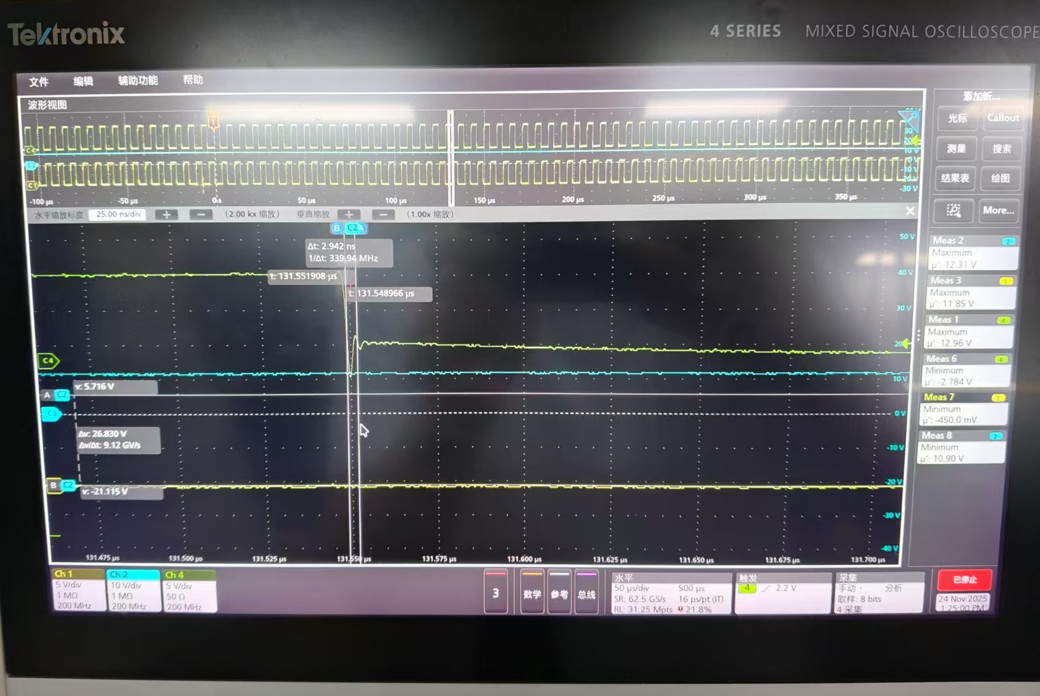

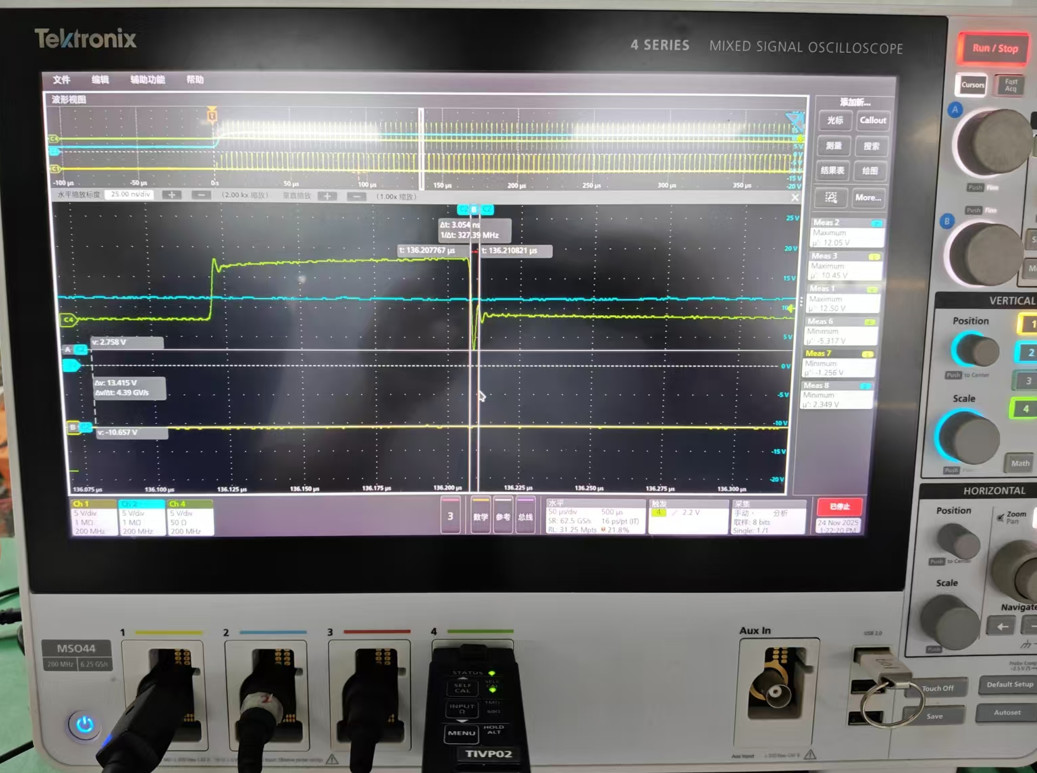

两个图片是启动和稳态时的波形。CH1:LO-VSS(光隔离探头) CH4:HO-HS(低压探头):

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,

请参考芯片数据手册“7.1 Absolute Maximum Ratings” 的注释1。长时间暴露在绝对最大额定条件下可能会影响芯片的可靠性。

建议走线尽可能短且直接,宽度保持至少 20mil。尽量保持栅极环路紧凑,以减少寄生电感。

对于 LO 走线,确保其经过连续的接地平面,使回流电流直接流过走线下方( 11 Layout) 。